### Bachelor's Thesis Nr. 290b

Systems Group, Department of Computer Science, ETH Zurich

A model-based approach to platform-level power and clock management

by

Jasmin Schult

Supervised by

Daniel Schwyn Dr. David Cock Prof. Dr. Timothy Roscoe

February 2020 - August 2020

#### Abstract

The correct management of a platform's power and clock resources is vital for the correct operation of the platform's hardware, which in turn forms the cornerstone of any assurances provided by software. In light of this, the firmware implementing such a power and clock management solution should ideally provide strong correctness guarantees. However, to the extent of our knowledge, the current state of the art does not go beyond manually-coded point solutions.

This thesis approaches the problem of power and clock management in a more principled fashion: It proposes a model that captures the behaviour of the platform in this management context. Additionally, a set of mechanisms are presented that, if applied to any model instance, generate management solutions for the platform described by that instance. If the correctness of these mechanisms were formally verified, which was not possible within the time constraints of this thesis, provably correct management solutions could be generated for any platform whose behaviour can be expressed by the model.

#### Acknowledgements

I would like to extend my heartfelt thanks to Daniel Schwyn, Dr. David Cock, Dr. Michael Joseph Giardino and Prof. Dr. Timothy Roscoe. Without them, this thesis would not have been possible, not only because they developed the fundamental idea behind it, but also because their support, suggestions and feedback was invaluable.

In light of this, it felt more natural to me to write the entirety of this thesis (with the exception of these acknowledgements) in the first-person-plural point of view. However, I do take full responsibility for any kind of mistakes or lack of clarity in the argumentations or descriptions.

# Contents

| 1 | <b>Intr</b> 1.1 | State of the Art                         | 8  |

|---|-----------------|------------------------------------------|----|

|   | 1.2             | Goal of this thesis                      | 9  |

| 2 | Rela            | ated Work                                | 10 |

|   | 2.1             | General related work                     | 10 |

|   |                 | 2.1.1 Power Management                   | 10 |

|   |                 | 2.1.2 BMC firmware                       | 10 |

|   |                 | 2.1.3 Related Problems                   | 11 |

|   | 2.2             | Enzian                                   | 11 |

|   | 2.3             | Sockeye                                  | 12 |

| 3 | Pow             | ver and Clock Management                 | 13 |

|   | 3.1             | Resources                                | 14 |

|   | 3.2             | Producers                                | 16 |

|   | 3.3             | Consumers                                | 17 |

|   | 3.4             | Managers                                 | 18 |

|   |                 | 3.4.1 Consumer Awareness                 | 19 |

|   |                 | 3.4.2 Producer control                   | 20 |

|   | 3.5             | Summary                                  | 21 |

| 4 | Def             | inition of Scope and Objective           | 23 |

|   | 4.1             | Scope                                    | 23 |

|   | 4.2             | The Objective                            | 25 |

|   |                 | 4.2.1 The Mechanism                      | 25 |

|   |                 | 4.2.2 The Model                          | 26 |

|   | 4.3             | Summary                                  | 26 |

| 5 | Mo              | delling the platform                     | 27 |

|   | 5.1             | Description of Structures                | 27 |

|   | 5.2             | General structure                        | 28 |

|   | 5.3             | Representation of conductor state        | 28 |

|   |                 | 5.3.1 Representation of a characteristic | 29 |

|   |                 | 5.3.2 Representation of state            | 29 |

|   | 5.4             | Producer Description                     | 30 |

|   |                 | 5.4.1 Producer Inputs                    | 33 |

|   |                 | 5.4.2 Outputs                            | 34 |

|   |     | 5.4.3   | Summary                                  | 38         |

|---|-----|---------|------------------------------------------|------------|

|   | 5.5 | Events  |                                          | 38         |

|   |     | 5.5.1   | Initiate and Complete events             | 39         |

|   |     | 5.5.2   | Ideal Static Management                  | 40         |

|   |     | 5.5.3   | Constructive Events                      | 41         |

|   |     | 5.5.4   | Event Relations                          | 43         |

|   |     | 5.5.5   | Sequence Requirements                    | 46         |

|   |     | 5.5.6   | Initiate Events                          | 18         |

|   |     | 5.5.7   | Sequence requirements for the MAX15301   | 50         |

|   |     | 5.5.8   | Summary                                  | 54         |

|   | 5.6 | Model   | $ m ling~the~I^2C~bus~\dots\dots\dots$ 5 | 55         |

|   |     | 5.6.1   | Operability indicator                    | 55         |

|   |     | 5.6.2   | Producer extensions                      | 55         |

|   |     | 5.6.3   | Default States                           | 57         |

|   |     | 5.6.4   | Issues                                   | 57         |

|   |     | 5.6.5   | Summary                                  | 59         |

|   | 5.7 | Consu   | mer Description                          | 30         |

|   | 5.8 | Platfor | $^{ m cm}$ Description                   | 31         |

|   |     | 5.8.1   | Conductor description                    | 32         |

|   |     | 5.8.2   |                                          | 35         |

|   |     | 5.8.3   | Summary                                  | 37         |

|   |     | 5.8.4   |                                          | 37         |

|   | 5.9 | Implic  | ${ m ations}$                            | 37         |

|   |     | 5.9.1   | Valid Platform States                    | 37         |

|   |     | 5.9.2   | Valid Event Sequences                    | 39         |

|   |     | 5.9.3   | Valid Consumer Transitions               | 71         |

|   |     | 5.9.4   | Summary                                  | 73         |

| 6 | Med | chanist | $_{ m ns}$                               | 74         |

|   | 6.1 | SAT     |                                          | 74         |

|   | 6.2 | State ( | Generation                               | 75         |

|   |     | 6.2.1   | Problem Definition                       | 75         |

|   |     | 6.2.2   |                                          | 77         |

|   |     | 6.2.3   | Algorithm                                | <b>7</b> 9 |

|   |     | 6.2.4   | Finding all solutions                    | 33         |

|   | 6.3 | Sequer  |                                          | 33         |

|   |     | 6.3.1   | Problem Definition                       | 33         |

|   |     | 6.3.2   |                                          | 34         |

|   |     | 6.3.3   | - •                                      | 38         |

|   |     | 6.3.4   |                                          | 90         |

|   | 6.4 | Consu   |                                          | 92         |

|   |     | 6.4.1   |                                          | 92         |

|   |     | 6.4.2   |                                          | 93         |

|   |     | 6.4.3   |                                          | 93         |

|   | 6.5 |         | $oldsymbol{\Theta}$                      | 95         |

| 7            | Mod  | delling | the Enzian                             | 96  |

|--------------|------|---------|----------------------------------------|-----|

|              | 7.1  | Overvi  | iew                                    | 96  |

|              | 7.2  |         | the Enzian platform is well-designed   | 97  |

|              |      | 7.2.1   | Monitoring Functionality               | 97  |

|              |      | 7.2.2   | I <sup>2</sup> C Buses                 | 97  |

|              |      | 7.2.3   | Enable Signals                         | 97  |

|              |      | 7.2.4   | Hierarchy                              | 99  |

|              | 7.3  | Depen   | idence of CPU and FPGA                 | 99  |

|              | 7.4  | The M   | Indelling process                      | 100 |

|              |      | 7.4.1   | Consumer Transitions                   | 100 |

|              |      | 7.4.2   | Sequence Generation                    | 100 |

| 8            | Imp  | lement  | tation                                 | 102 |

|              | 8.1  | Model   | syntax                                 | 102 |

|              |      | 8.1.1   | Conductor States                       | 102 |

|              |      | 8.1.2   | State Requirements                     | 103 |

|              |      | 8.1.3   | Complex constraints                    | 103 |

|              |      | 8.1.4   | Default States                         | 103 |

|              |      | 8.1.5   | Representation of Events               | 104 |

|              |      | 8.1.6   | Consumer Transitions                   | 104 |

|              | 8.2  | Mecha   | unism Implementation                   | 104 |

|              |      | 8.2.1   | State Generation                       | 104 |

|              |      | 8.2.2   | Sequence Generation                    | 107 |

|              |      | 8.2.3   | Consumer Demand Generation             | 108 |

|              |      | 8.2.4   | Implementation boundaries              | 108 |

| 9            | Eva  | luation | 1                                      | 111 |

|              | 9.1  | Perform | mance of our Mechanisms                | 111 |

|              |      | 9.1.1   | Online Static Management               | 111 |

|              |      | 9.1.2   | Offline Static Management              | 123 |

|              | 9.2  | Compa   | arison to existing management solution | 125 |

|              | 9.3  | Conclu  | usion                                  | 132 |

| 10           | Con  | clusio  | $\mathbf{n}$                           | 134 |

|              | 10.1 | Summ    | ary                                    | 134 |

|              |      |         | e Work                                 | 135 |

| $\mathbf{A}$ | Eva  | luation | n $3$                                  | 139 |

|              | A.1  | Manua   | ally generated sequence                | 139 |

|              | A.2  | Auton   | natically generated sequence           | 140 |

|              |      | Compa   |                                        | 141 |

# List of Tables

| 5.1  | Representation of structures                                                  |

|------|-------------------------------------------------------------------------------|

| 5.2  | Representation of structure instances                                         |

| 5.3  | The discretisation of stable characteristics                                  |

| 5.4  | The Conductor State structure                                                 |

| 5.5  | The Producer structure                                                        |

| 5.6  | The Input structure                                                           |

| 5.7  | The Output structure                                                          |

| 5.8  | The State Possibility structure                                               |

| 5.9  | The State Requirement structure                                               |

| 5.10 | A Producer instance for the MAX15301                                          |

| 5.11 | An example static management action                                           |

|      | An example assignment of Initiate and Complete events                         |

| 5.13 | The Event Graph structure                                                     |

| 5.14 | The Initiate Event structure                                                  |

| 5.15 | A State Possibility instance defined by a MAX15301                            |

| 5.16 | The Event Graph instance for $P1 \rightarrow P4$                              |

| 5.17 | The Event Graph instance for $P2 \rightarrow P3$                              |

| 5.18 | The Event Graph instance for $P1 \rightarrow P1$                              |

| 5.19 | The Event Graph instance for P2, P4 $\rightarrow$ P1                          |

| 5.20 | The Producer instance for an $I^2C$ bus                                       |

| 5.21 | Adding the bus operability indicator to a bus-compliant Producer instance 56  |

| 5.22 | A symbolic State Possibility instance                                         |

| 5.23 | How to include bus operability in the above State Possibility instance 56     |

|      | The Consumer structure                                                        |

| 5.25 | The Platform structure                                                        |

| 5.26 | The Connection structure                                                      |

| 5.27 | An example Connection instance                                                |

| 5.28 | The Conductor structure                                                       |

| 5.29 | The construction of a Conductor instance                                      |

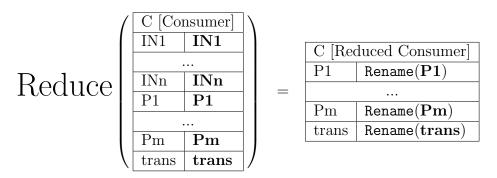

| 5.30 | Reduce applied to a State Possibility instance                                |

| 5.31 | Example Input and Output descriptions                                         |

| 5.32 | A Conductor instance corresponding to the above pin and Platform instances 65 |

| 5.33 | The original Consumer structure compared to the Reduced Consumer              |

|      | structure                                                                     |

|      | Reduce applied to a Consumer instance                                         |

| 5.35 | The Reduced Platform structure                                                |

| 5.36 | An illustration of the platform reduction process                             |

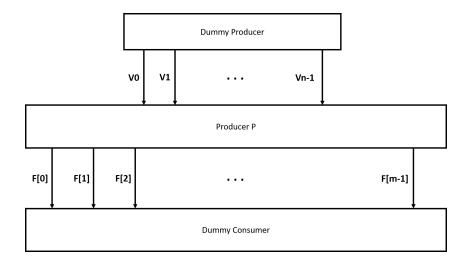

| 6.1 | The j-th State Possibility P defines for its output F[i]     | 78  |

|-----|--------------------------------------------------------------|-----|

| 6.2 | The Platform instance representing F                         | 78  |

| 6.3 | The Events function that represents formula F                | 87  |

| 6.4 | A symbolic Initiate Event instance                           | 88  |

| 6.5 | Two equivalent approximate Initiate Event instances          | 89  |

| 6.6 | An example DP table                                          | 94  |

| 8.1 | An example stack of execution states                         | 105 |

| 8.2 | The set of flags that can be passed to the mechanisms        | 110 |

| 9.1 | An overview of problem instances P1 to P3                    | 114 |

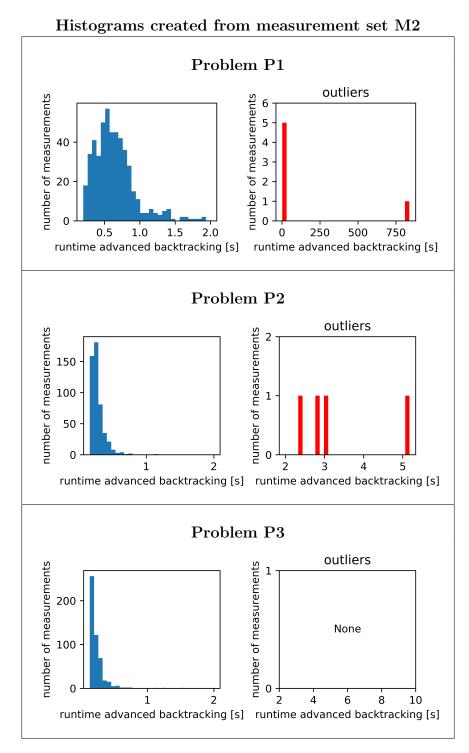

| 9.2 | Histograms of the data collected in M2                       | 119 |

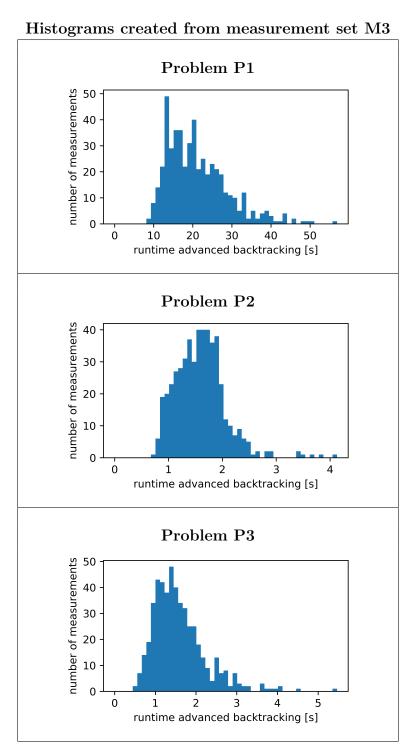

| 9.3 | Histograms of the data collected in M3                       | 120 |

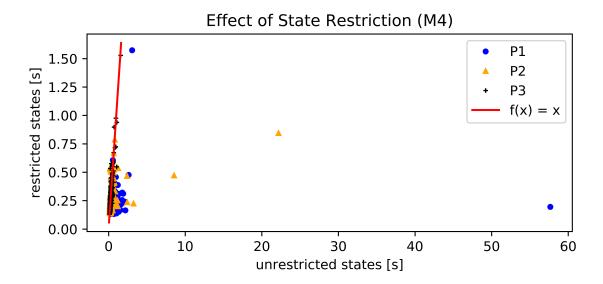

| 9.4 | The number of solutions for restricted P1 to P3              | 122 |

| 9.5 | Overview of problem instances P1 to P6                       | 124 |

| 9.6 | Measurements for P1 to P6                                    | 125 |

| 9.7 | Summary of command set comparison in appendix table A.1      | 130 |

| A.1 | A comparison of the commands found in the two boot sequences | 143 |

# List of Figures

| 3.1         | Relations between producers, consumers and managers                                         | 14       |

|-------------|---------------------------------------------------------------------------------------------|----------|

| 5.1         | An example platform instance                                                                | 29       |

| 5.2         | The MAX15301's pin layout                                                                   | 32       |

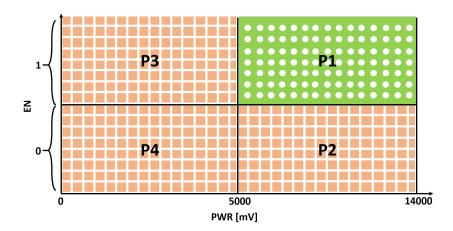

| 5.3         | Level plot of the input/output relations of a MAX15301                                      | 36       |

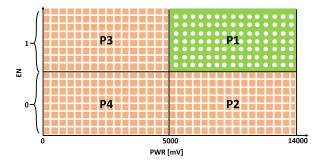

| 5.4         | State Possibilities of the MAX15301 as level plot regions                                   | 36       |

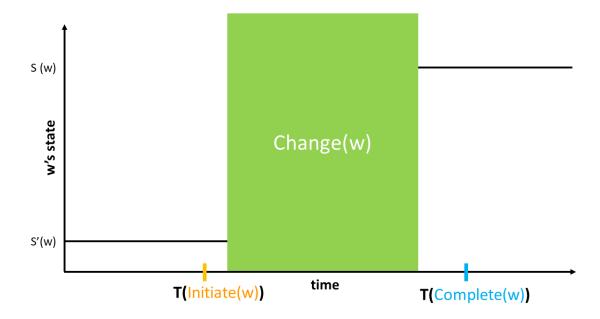

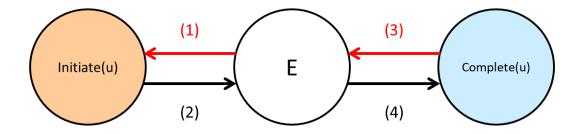

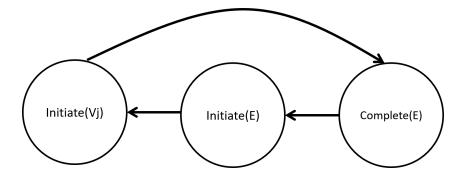

| 5.5         | The timing relation between Initiate and Complete events                                    | 43       |

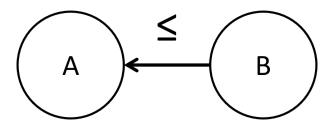

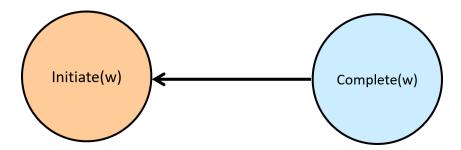

| 5.6         | An example graph representation of events                                                   | 44       |

| 5.7         | The timing relation between Initiate and Complete events as a graph                         | 44       |

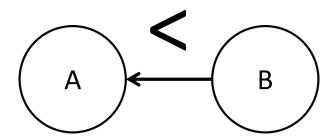

| 5.8         | An overview of possible event restrictions                                                  | 45       |

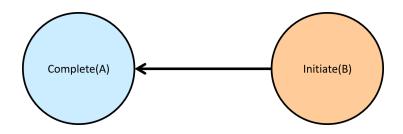

| 5.9<br>5.10 | The correct interpretation of edges in event graphs                                         | 46<br>48 |

| 5.10        |                                                                                             | 40       |

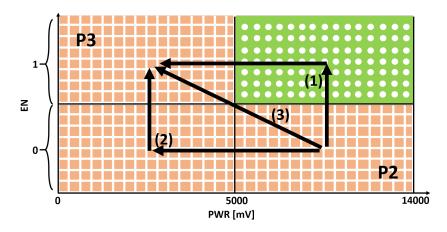

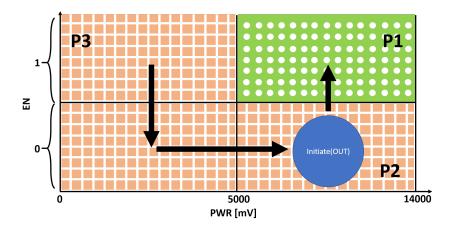

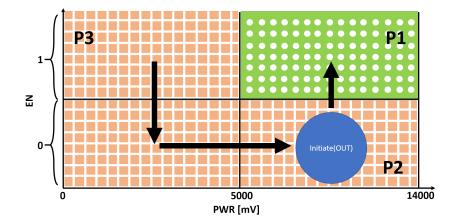

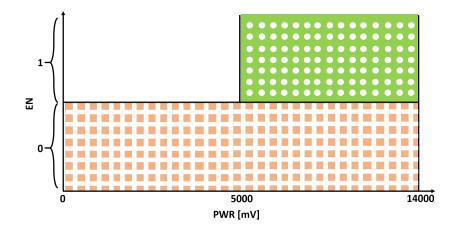

|             | Possible transitions from P2 to P3 within the MAX15301's level plot                         | 51       |

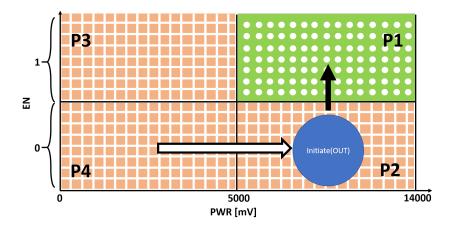

|             | Possible transitions from P2 or P4 to P1 within the MAX15301's level plot                   | 53       |

|             | Possible transitions from P3 to P1 within the MAX15301's level plot                         | 54       |

|             | Platform instance illustrating the issue with bus commands that pull the                    | 0 1      |

| 0.10        | bus low                                                                                     | 58       |

| 5.16        | A Platform instance illustrating the issue of a transiently available bus .                 | 59       |

|             | An example platform instance illustrating Connections                                       | 62       |

|             | An Platform instance illustrating the construction of a Conductor instance                  | 64       |

| 6.1         | Schematic representation of the platform used to represent F                                | 77       |

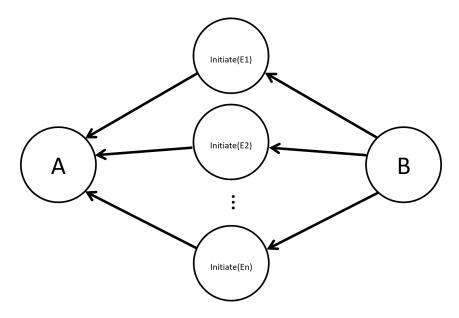

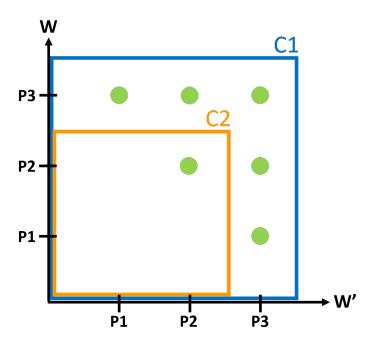

| 6.2         | An illustration for the need of complete consumer demands                                   | 81       |

| 6.3         | Graph illustrating why the first two cases of Seq(Vj) are disjoint                          | 85       |

| 6.4         | Schematic illustration of a conductor change                                                | 85       |

| 6.5         | An illustration of the correspondence between truth assignments and tim-                    |          |

|             | ing relations to Change(E)                                                                  | 85       |

| 6.6         | The two options that render clause $F[j]$ true $\ldots \ldots \ldots \ldots$                | 86       |

| 6.7         | Graph representation of our approximation of the Implicit Event I                           | 89       |

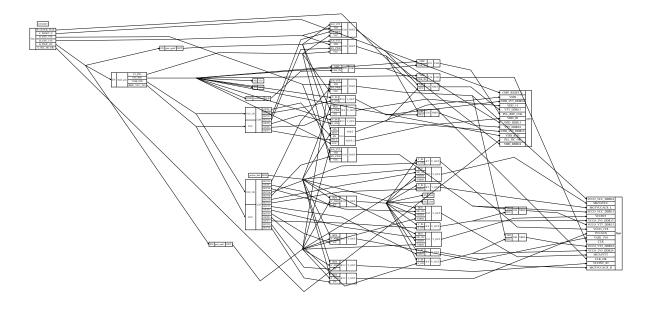

| 7.1         | An illustration of the Enzian platform                                                      | 96       |

| 7.2         | Simplification of the MAX15301's State Possibilities possible on the Enzian $$              | 99       |

| 8.1         | The consequences the choice of State Generation mechanism has                               | 108      |

| 9.1         | An illustration of the fact that a reduced search space does not imply increased efficiency | 113      |

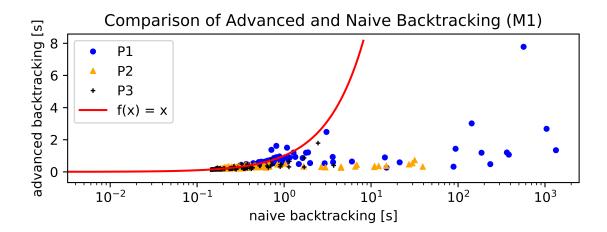

| 9.2 | A performance comparison of the backtracking mechanisms                      | 117 |

|-----|------------------------------------------------------------------------------|-----|

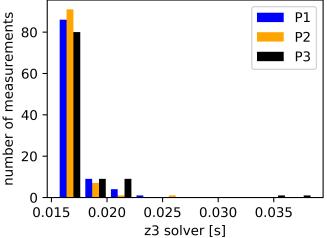

| 9.3 | A Histogram of runtime measurements of the Z3-solver                         | 118 |

| 9.4 | Effect of state restriction on the performance                               | 123 |

| 9.5 | A visualistion of different consumer transition interleavings                | 126 |

| 9.6 | Definitions of sets of interest in the comparison of $S_{gen}$ and $S_{man}$ | 128 |

| 9.7 | Clock configurations in manual boot sequence                                 | 132 |

## Chapter 1

## Introduction

To some extent, every piece of software relies on the underlying hardware platform to function correctly. Even formally verified software is no exception; as noted by Klein et al in the discussion of their verification of seL4 ([15], p. 29):

The best validated formal theorem will not guarantee correct behaviour if processor and memory are melting underneath.

There are several ways in which the correct functionality of hardware can be undermined. For instance, by applying an inappropriate supply voltage or a too skewed clock signal that violates the circuitry's timing constraints. Consequently, the *correct* management of the platform's power and clock resources constitutes a vital precondition for any software guarantees to hold.

This thesis attempts to make a step towards providing stronger guarantees for the correctness of this management. Before we concretise this goal, we discuss the current state of the art of power and clock management.

#### 1.1 State of the Art

On modern computing platforms, power and clock management is not a trivial matter. A CPU might for instance require an array of different supply voltages that must come online in specific sequences during the bootstrap process. Therefore, this management along with other general platform maintenance functionality is handed off to a dedicated microcontroller. Depending on vendor and platform, this microcontroller is known under many names, for example *Management Engine* in the case of Intel. In this thesis, we will use the more general term *Baseboard Management Controller* (BMC).

The general state of the firmware running on BMCs, as far as disclosed, is at odds with the high level of privilege with which it executes [6]. This is also includes the parts dedicated to power and clock management: To our knowledge, the current published state of the art does not go beyond manually-coded point solutions and no attempts at formal verification have been made.

#### 1.2 Goal of this thesis

In this thesis, we will approach the problem of power and clock management in a fashion that separates policy from mechanism: We devise a model that captures *correct* and relevant platform behaviour with respect to power and clock management. On top of this model, we construct a set of mechanisms that generate the BMC actions necessary to correctly manage the platform described by any model instance.

Our approach is promising from the point of view of formal verification: If we prove the correctness of the mechanisms with respect to the intended model semantics, we can generate verified management code for any platform our model can capture. Within the time constraints of this thesis, we were not able to completely formalise our model semantics and perform this correctness proof, yet we are convinced that it would be possible.

We conclude this section by outlining the structure of our thesis and the purpose every chapter serves with respect to our management approach:

In chapter 3, we attempt to describe power and clock management as well as the involved components from a point of view that is as universal as possible. Since we have found almost no suitable literature to rely on, we complete this description with observations we have made in context of the Enzian research platform, which we will introduce in chapter 2, along with other scientific work that relates to this thesis.

Based on these general descriptions, we identify a subset of power and clock management our thesis will focus on in chapter 4. We then proceed to concretise the requirements our model and mechanisms must fulfil.

Chapter 5 presents the platform model we have devised, motivated by our earlier general description of power and clock management.

In chapter 6, we concretise the problems our mechanisms must solve and discuss their computational complexity. We then present an algorithm capable of providing the desired solution.

As a proof of concept, we have modelled the aforementioned Enzian platform. In chapter 7, we present some observations we have made in that process, as well as some general modelling advice.

Chapter 8 is dedicated to the implementation of our mechanisms as well as the model syntax.

We evaluate the performance of our mechanisms and perform a comparison to the management solution implemented for the Enzian platform in chapter 9.

Finally, we conclude our thesis and propose future work in chapter 10.

## Chapter 2

## Related Work

This chapter discusses the scientific work relevant for this thesis. After an overview of general related work, we will introduce two current projects of the Systems Group at ETH that have shaped the idea for a policy-mechanism separated approach to power and clock management.

#### 2.1 General related work

We have structured this section into several subsections according to the discussed topic.

#### 2.1.1 Power Management

The topic of optimally trading off performance and power consumption has been thoroughly studied. In scientific literature [3, 4], the process of deciding when a CPU or similar computational agent should be transitioning to a more or less performant power state is referred to as dynamic power management. This does not correspond to the power management problem we address in this thesis; we are concerned with platform-level power and clock management: The firmware running on the BMC must realise the aforementioned transitions between power states but does not make the decision of when to perform them.

#### 2.1.2 BMC firmware

As mentioned in the introduction, the current state of the firmware running on BMCs is not satisfactory. In recent years, the disclosure of multiple resulting security vulnerabilities has drawn a lot of attention to this issue. As a consequence, first actions have been taken to improve the situation, of which we provide a non-comprehensive, high-level overview:

Up to a few years ago, BMC firmware was proprietary and not disclosed to the public. Since then, projects such as OpenBMC and u-bmc have disclosed some implementations to the public, with the aim of providing more transparency and in the hopes of collectively finding and fixing bugs and vulnerabilities. [9]

To ease data centre management, modern BMCs offer an array of remote management capabilities. To be able to do so, the firmware must implement some minimal OS functionality such as NIC drivers and network protocols. According to Narayanan et al, the resulting inherent complexity of the firmware code routinely introduces bugs and vulnerabilities. To address this issue, they propose the verified minimal OS *RedLeaf* in [17], that is "aimed at the needs of a diverse family of firmware subsystems".

In 2018, the National Institute of Standards and Technology (NIST) of the United States has released a set of guidelines to improve the protection as well as the detection and subsequent recovery of platform firmware from malicious attacks. [19]

#### 2.1.3 Related Problems

As mentioned in the introduction, we aim to devise a model that captures *correct* platform behaviour. Quite generally, this can be achieved by placing appropriate *constraints* on said behaviour. The mechanisms we construct to extract management actions from our model therefore correspond to *Constraint Satisfaction Problems* (CSPs).

CSPs are a very broad class of problems. In the resulting wealth of scientific papers about these problems, one could almost certainly find a CSP formulation for a different problem that is very similar in character to the platform model we have devised. Thematically, we have found the most similar CSP instances to be concerned with the so-called *unit commitment problem* (see, for instance, [26]). Said is concerned with determining the optimal start-up and shut-down times of generating units in connection with electrical power production. However, these problem instances do not exhibit much structural similarity to our platform model.

#### 2.2 Enzian

Until recently, commercial off-the-shelf hardware (CTOS) was ubiquitously used, from every-day to commercial usage. Nowadays, there is an increasing trend towards highly specialised or even custom hardware for commercial applications. This is problematic for academic systems software research: research on CTOS hardware does not generalise to custom hardware whereas custom hardware - if even disclosed - features such a high degree of specialisation that research is likely reduced to confirming that it works well for the intended use case but badly for others. [25]

This is where Enzian comes into play, a research platform built from scratch by the Systems Group at ETH. Its most extraordinary feature is the tight coupling of a server-class ThunderX CPU with a high-end FPGA. This coupling, combined with the configurability of the FPGA offers a tremendous amount of flexibility and can therefore be used to explore and simulate a lot of scenarios interesting to systems software research.

With its high-end CPU and FPGA, power and clock management on the Enzian platform is inherently non-trivial, and it thus also features a BMC. With the Enzian being designed from scratch, its complete platform layout and the functionality of every integrated circuit

are revealed. This offers a unique opportunity to reason about and explore the power and clock management actions the Enzian BMC must perform.

## 2.3 Sockeye

Sockeye is another on-going research project of ETH's Systems Group. Originally, *Sockeye* referred to the domain specific language developed by Daniel Schwyn in his master's thesis [22] to express the *address decoding net* model proposed by [2]. Meanwhile, Sockeye has evolved to a full-fledged research project that seeks to formalise the interface between software and hardware to ultimately generate provably correct code that handles the delicate interaction with today's complex hardware.

The combination of the idea behind Sockeye and the insights into BMC management provided by the Enzian platform have given rise to the model-mechanism based approach to power and clock management pursued in this thesis.

## Chapter 3

## Power and Clock Management

In this chapter, we take a closer look at how power and clock management is conducted in a modern computer system, setting the scene for the work and results of this thesis. Over the course if this chapter, we flesh out several observations, assumptions and definitions about power and clock management that we will refer to when motivating design choices in our later work.

Literature on power and clock management from a general perspective is very scarce. As already mentioned in the introduction, most of the following discussion is hence based on observations made in connection with the Enzian platform.

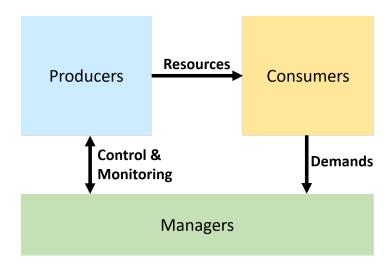

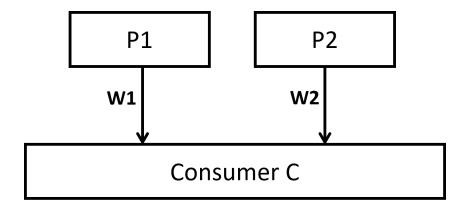

This chapter is structured as follows: In the first section, we define clock and power resources and develop a more concrete perspective on the concept of *power and clock management*. In subsequent sections, we approach the topic from a functional point of view. We identify and elaborate on the entities in a computer system that adopt the following management roles (see figure 3.1 for a schematic overview):

- producers that supply specific resources (section 3.2)

- consumers that require specific resources (section 3.3)

- managers that are balancing the demands of the consumers and the supply of the producers (section 3.4)

In order to simplify the reasoning about all entities involved in power and clock management, we furthermore define the term platform, inspired by [10], and component in the context of this thesis as follows:

**Definition 1** (Platform). A platform is the composition of all producers, consumers and managers present in a computer system.

**Definition 2** (Component). A component is a single producer or a consumer.

Figure 3.1: A schematic overview of the relation between producers, consumers and managers

The Component definition purposely excludes managers, since the platform model we are going to develop over the course of the next three chapters adopts a manager's perspective on the platform.

#### 3.1 Resources

In the context of this thesis, a resource is defined as follows:

**Definition 3** (Resource). A resource is a clock signal, a logical signal or a power source.

**Remark.** From a technical point of view there is no difference between a conductor supplying power and one that is transmitting a logical signal. In this thesis, we are going to use the term *logical signal* in situations where only the interpretation of the power signal as being high or low is of import.

Clock signals and power are transmitted over some conductor, in computer systems this is most commonly a wire or a circuit trace.

**Remark.** In the context of this thesis, we refer to *conductor* strictly in a power and clock management context. When referring to a conductor, we thus always mean a conductor that is supplying a clock signal or power to the platform.

From an alternate perspective, we could consider a conductor to embody the corresponding resource. Power and clock management hence translates to managing the state of conductors.

Before we can define Power and Clock Management for our purposes, we need to think about our performance metric. Management objectives are usually tied to some performance metric that is used to compare and evaluate different management strategies.

Power and clock resources are critical in the sense that providing a component with a wrong input can be devastating. For this reason, components usually define the following electrical specifications:

- absolute maximum ratings: constraints that must be observed at all times to prevent the component from taking permanent damage

- recommended operating conditions: stricter constraints that must be observed to ensure the correct operation of a component.

Based on these specifications, we define the term *input constraints* as follows:

**Definition 4** (Input Constraints). At any given point in time, the input constraints of a component are defined by its *recommended operating conditions* if the component is supposed to be operational at this point and its *absolute maximum ratings* otherwise.

**Remark.** We refer to these constraints as *input* constraints since in all generality, a component can exert no direct control over its inputs, while it can very well influence the character of its outputs. For this reason, both absolute maximum ratings and recommended operating conditions are mainly concerned with the component's inputs.

For the reasons mentioned above, we argue that in a power and clock management scenario, meeting all input constraints takes priority over the usual efficiency and utilisation criteria.

In the remainder of this thesis, we hence will adopt this more concrete view on power and clock management:

**Definition 5** (Power and Clock Management). Power and Clock Management is concerned with managing the *state of conductors*, in a fashion that respects every component's input constraints while satisfying consumer demands.

**Remark.** On some platforms, there might exist certain consumer demands that cannot be fulfilled without violating any input constraints. In the context of this thesis, we assume that power and clock management is allowed to *fail* by refusing to comply in the face of such demands, rather than striving to provide a good approximation.

The state of conductors is given by their measurable electrical characteristics such as voltage, frequency and current. Commonly, voltage and frequency can be regulated to a stable, static value by the platform's producers. The current that is flowing across a conductor at any given point in time, however, depends on the dynamic power requirements of the attached components. These are in turn determined by the load the system is experiencing.

Because of this difference, we refer to voltage and frequency as *stable* conductor characteristics whereas current is *volatile*.

Using these concepts, we can further classify power and clock management into two different categories:

**Definition 6** (Static Power and Clock Management). Static Power and Clock Management is about managing the *stable* characteristics of conductors.

Static Power and clock management can be accomplished directly by appropriately configuring the outputs of the platform's producers.

**Definition 7** (Dynamic Power and Clock Management). Dynamic Power and Clock Management handles exceptional platform events. This includes general platform failures as well as *volatile* platform characteristics reaching critical levels.

This is usually accomplished as follows: the overall status of the platform is continuously monitored. Whenever a fault or alert condition is detected, appropriate countermeasures are taken. If, for instance, the current across a conductor exceeds a certain threshold, power-limiting measures such as CPU throttling or an emergency shutdown are initiated.

#### 3.2 Producers

From a physical point of view, the term *transformer* might be more appropriate than *producer*: Naturally, any entity providing power or clock signals also consumes power in one form or another. In our management context, we use the concept of a *producer* with respect to an entity's main purpose in the context of the platform and hence define it as follows:

**Definition 8** (Producer). A producer is an entity whose main purpose is the production of platform resources, i.e. specific states on power or signal-carrying conductors.

In a modern computer system, producers are electronic circuits such as power supplies, voltage regulators, oscillators and clock generators.

As described in [16], clock producers usually form a so-called Clock Tree. Similarly, for several reasons that are detailed very concisely in ([10], p. 121), producers concerned with power resources are commonly arranged in a multi-level hierarchy. This results in the following observation:

**Observation 9.** Producers are arranged in hierarchies.

We conclude this section with some more observations we have made when surveying the producers present on the Enzian's platform.

A producer is usually a distinct unit that is soldered onto the circuit board. The structure of a producer is defined by the fixed layout of its pins, which are used to integrate the producer into the platform by connecting the appropriate conductors. The purpose of a pin and if it serves as an input or output is specified in the producer's manual.

**Observation 10.** Producers feature a fixed set of pins that can be connected to conductors. Each pin serves a pre-defined purpose.

Generally, producers are focused on providing *stable* states on the conductors connected to their output pins. They normally do so using a feedback loop that takes corrective actions if the true value deviates too much from the required one.

**Observation 11.** When directed to supply a certain value of a stable conductor characteristic, a producer will continue to output this particular value until it is told otherwise, unless a fault condition occurs.

Having multiple, independent producer regulate the state of the same conductor does not make a lot of sense; imagine two producers attempting to regulate the voltage across said conductor to different values. An exception to this is the case where all such producers can only be regulated jointly; for instance the up to four slaves operated by a MAX20751. However, in such a situation we would also be modelling all such producers as a single, joint producer. Thus we arrive at the following observation:

**Observation 12.** Any platform conductor's state is generated by at most one producer. Consequently, any conductor is an output to at most one producer.

The next conductor state a producer is required to provide is usually difficult to anticipate; a user might press the power or sleep button at an arbitrary point in time and a sudden increase in a CPU's workload might prompt it to request an increase in its clock speed. For this reason, a producer should be able to provide the whole range of output states it can offer at any given point in time, regardless of the previous input and command history.

**Observation 13.** In most situations, the range of output states a producer can provide is only dependent on its current inputs and *not* on its previous input and command history.

**Remark.** There are situations where this is not the case, most notably in connection with bus communication. See section 5.6 for a detailed discussion of this.

#### 3.3 Consumers

**Definition 14** (Consumer). A consumer is an entity of the computer system that needs to be supplied with specific power and clock inputs but is itself not mainly concerned with the production of platform resources.

**Remark.** Contrasting this definition with said of a producer (Definition 8) it is clear that the two are deliberately mutually exclusive.

The granularity of what is considered to be a single consumer is a matter of perspective. On the Enzian, we could for instance identify the ThunderX CPU, its DRAM banks and I/O ports as one consumer entity. In terms of complexity, consumers are commonly several levels above comparatively simplistic producers and require much more specific power and clock inputs.

We conclude this section by making a few more observations about the nature of consumers. Again, as in the producer section, these are based on the Enzian platform.

With the introduction of dedicated hardware for power and clock management, such as BMCs, consumers can be designed in a platform-independent manner. It follows that:

**Observation 15.** Apart from interfaces to managers and the state of conductors serving as inputs, the platform is generally transparent to consumers.

In order to receive the correct inputs, consumers thus impose specific demands on them. (See section 3.4.1 for a discussion on how said demands might be communicated to the platform's managers.) Some such demands are the result of different power states a consumer can adopt:

**Observation 16.** Consumers usually define a set of power states and transitions between them. Each such power state and each transition step is associated with very specific power and clock inputs that the consumer requires in that particular situation.

For example, the ThunderX's manual defines a 7-step power-up sequence that has it transition from a *powered-down* to a *powered-on* state ([7], p. 1827).

Furthermore, inputs to powered-on consumers can usually be fine-tuned to achieve different efficiency and performance trade-offs; an example for this is frequency and voltage scaling. Hence:

**Observation 17.** A consumer might also dynamically demand changes to its inputs, for instance in response to changes of its workload.

**Remark.** Although it would be more precise to say that the *software* running on a consumer requests such dynamic changes, this distinction is not required for our purposes.

We have yet to discuss the meaning of consumer demands from a time perspective. Conceptually, a consumer demand is fulfilled if the state of the consumer's input conductors agrees with the demand. In the context of power and clock management, it is quite obvious that only transiently adhering to a demand is insufficient; a single voltage pulse will clearly not be able to adequately power a CPU. It hence follows that a consumer demand needs to be imposed on the corresponding input conductor state permanently, until it is replaced by a more recent demand.

**Observation 18.** Consumer demands remain in effect until replaced by more recent demands.

**Remark.** This nicely coincides with observation 11.

### 3.4 Managers

This section discusses the manager role of the platform, including the instruments and mechanism a manager commonly has at its disposal to fulfil its purpose.

**Definition 19** (Manager). A manager is an entity concerned with the provisioning of correct conductor states. It is aware of the consumer demands and controls and configures the producers accordingly.

As stated in the introduction, the BMC is commonly heavily involved in this manager functionality. Since we wish to explore power and clock management strictly in the context of the BMC, we need to make the two assumptions about our platform.

#### **Assumption 20.** There is exactly one manager on the platform.

Nothing prevents the aggregation of multiple managers in a single system. However, letting the same resource be managed conjointly by several managers will most likely result in redundancy and inefficiency, so by stretching the definition of *platform* a bit, we could most likely identify different, possibly hierarchical management domains that we could consider to be individual platforms. For the purposes of this thesis, however, we will think of our computer system to be a *regular* server system featuring a single manager entity.

#### **Assumption 21.** This manager is a BMC.

That this is the case is not set in stone either: the ThunderX for instance, was originally intended to provide a *Voltage Regulator Module* that would assume direct control of the voltage regulator supplying the CPU's core voltage ([7], chapter 40).

This has another implication for the BMC: In general, it cannot manage its own power and clock inputs, since said are commonly a pre-condition for the BMC's management firmware to be able to run correctly. It hence follows that:

#### **Observation 22.** The BMC is not a consumer of the platform it is managing.

**Remark.** As mentioned in the introduction, the BMC is itself a microcontroller of non-negligible complexity. This of course raises the question: who is managing the BMC's power and clock inputs? This might be the task of another, simpler management domain from the perspective of which the BMC is a regular consumer. Or, alternatively, such inputs might be provided in an *always on if the computer system is plugged in* fashion. In any case, the bootstrapping and input management of the BMC is out of the scope of this thesis.

Making use of the above assumptions, we can now discuss the management mechanisms and instruments of a BMC specifically. We split this discussion into two parts, one concerned with consumer awareness and the other with how the BMC exerts control over the producers.

#### 3.4.1 Consumer Awareness

To correctly manage the platform, a BMC must be aware of the consumer's power and clock demands. This happens either in an active fashion, whereby the consumer actively communicates with the BMC or in a passive manner using hard-coded information.

#### Consumer - BMC communication

There is a variety of different interfaces that seek to enable consumer-BMC communication. The most prevalent such interfaces include the Advanced Configuration and Power Interface (ACPI) [8] and the Platform Environment Control Interface (PECI) ([10], p. 97). Also notable is the Intelligent Platform Management Interface (IPMI) [14], although said aims to provide remote management capabilities to system administrators rather than enabling consumer-BMC communication.

#### Hard-coded information

By definition, consumer requirements cannot always be obtained in an active manner: an integral part of power management is the correct bootstrapping of consumers, during which they commonly are not able to communicate their power requirements. Therefore, the bootstrapping requirements are defined in the corresponding consumer's manual and are typically hard-coded into the BMC's management firmware.

#### 3.4.2 Producer control

Successful power and clock management requires two-way communication between the BMC and the producers: In the context of static management, the BMC must be able to transmit commands to correctly configure the producers. In order to perform dynamic management, it must be able to receive feedback from them to continually monitor the platform activity and react to potential failures.

How exactly this communication is realised is subject to the platform's design and the nature of the producers.

Enzian relies primarily on the general purpose input/output (GPIO) pins exposed by the BMC. These pins are configurable by the software running on the BMC and can be used as detailed in the following subsections.

#### GPIO as output

GPIO pins can serve as both logical inputs and outputs. If a pin is configured to be used as an output, the management software can set the pin's logical level to either high or low. In such a case, we could argue that the BMC itself also adopts the role of a producer, since the production of such a logical signal constitutes an integral part of its management purpose. We thus arrive at the following observation:

#### **Observation 23.** The BMC is a producer

#### GPIO as input

A logical input to the BMC can by itself only provide a very limited amount of information (high or low) and is hence commonly used as alert or fault signal, to indicate

an (imminent) producer failure. As part of dynamic power and clock management, the BMC will then appropriately react in an event-based manner.

#### GPIO and I<sup>2</sup>C bus lines

GPIO pins can also be connected to I<sup>2</sup>C bus communication lines. I<sup>2</sup>C is a bus communication protocol that allows communication between multiple devices connected to the bus. Quite a few producers are I<sup>2</sup>C compliant, most by implementing the higher level System Management Bus (SMBus) or Power Management Bus (PMBus) protocols that build on I<sup>2</sup>C and SMBus respectively.

Every such bus-compliant device defines a set of commands that the BMC can issue, both to query the current status of the device, including the readings of any integrated sensors, and to control its power or clock outputs. The I<sup>2</sup>C bus is thus an instrument that can be used in both a dynamic as well as a static management context.

The situation is, however, not quite as simple as it seems at first glance. The reason for this is  $I^2C$ 's solution to the following problem: If several devices concurrently try to pull the line up to transmit a 1 and pull it to ground to transmit a 0, this may cause a short circuit.

I<sup>2</sup>C avoids such a scenario as follows: Every bus line is pulled up to a supply voltage level using a pull-up resistor. In order to communicate, devices may only pull the line low. [11] At the same time, the I<sup>2</sup>C specification does not prevent powered-off devices from pulling the bus lines low, which effectively renders the bus unusable until all such devices are powered.

**Observation 24.** The I<sup>2</sup>C bus is not necessarily operational if any connected devices are powered off.

### 3.5 Summary

In this chapter, we have discussed platform-level power and clock management. We have realised that there is a direct correspondence between the resources managed in this context and the state of platform conductors. We have then identified two types of physical characteristics that comprise the state of such conductors: stable characteristics that can be regulated to fixed values by the platform, and volatile characteristics that change dynamically. Based on this distinction, we have subcategorised power and clock management into static and dynamic management.

Additionally, we have defined three relevant roles in this management context: Producers, Consumers and Managers. Using the Enzian platform as an example, we have made some observations about the general nature and behaviour of entities adopting these roles. We have discussed the means platform managers have at their disposal to monitor and communicate with the other components. With the observation that  $I^2C$  buses are not

necessarily operational, we have encountered a first subtle issue that our management solution must address.

## Chapter 4

## Definition of Scope and Objective

In this chapter, we concretise the scope of operation and the objective of the thesis.

### 4.1 Scope

In this thesis, we are only going to address the topic of *Static Power and Clock Management*, as it is defined in section 3.1. The reason for this is that, assuming ideal conditions and every component working as expected, static management is sufficient to correctly operate the platform. However, it goes without saying that in a *real* setting, the correct handling of potentially catastrophic events as performed by dynamic management is extremely important for platform reliability and safety and must not be omitted.

As already hinted at, for static management to be reasonable by itself, we need to make the following assumption.

**Assumption 25.** The platform is operating as expected and no exceptional events are occurring.

Thus, neither input constraints nor consumer demands involving *volatile* characteristics are of any concern to us. In order to simplify our reasoning about static management, we redefine the *state* of a conductor to only refer to its *stable* characteristics.

Based on the definition of stable characteristics, as well as our assumptions about the BMC being the platform's only manager, we can furthermore make the following assumption:

**Assumption 26.** Once the BMC stops altering the configuration of producers, the state of the platform's conductors will eventually stabilise and will remain unchanged until the BMC issues further changes.

If all of the platform's conductors feature such a stabilised state, we will call the collection of all such states a *stable platform state*. For the purposes of this thesis, we are in need of two more assumptions:

#### Assumption 27. Consumer demands are time-invariant.

It is not unusual for power sequences to feature timing constraints. The power-up sequence of the ThunderX, for instance, requires that a signal indicating *clock readiness* is asserted at least 3 milliseconds after the corresponding clock input has stabilized at its target frequency [7].

For our purposes, however, we are going to incorporate such timing requirements in the scheduling of consumer demands rather than the demands themselves. In the case of the ThunderX, we will only begin to fulfil the demand "Assert clock readiness" when at least 3ms have passed since we have reached a stable platform state after fulfilling the demand that had the clock input transition to the mentioned target frequency.

**Assumption 28.** Consumer demands are not associated with any real-time constraints. In particular, the BMC is allowed to wait until the platform has reached a stable state before issuing further changes.

Arguably, most timing-sensitive tasks belong to the dynamic power and clock management domain, which renders this assumption not unrealistic. Furthermore, considering the platform-independent design of consumers (as indicated by observation 15), adding very harsh real-time constraints to power sequences will severely limit the range of platform designs that will be able to uphold said, and will thus most likely be avoided if possible. Indeed, on the Enzian platform neither the ThunderX's nor the FPGA's power sequences feature any real-time constraints.

In spite of this assumption, we consider a static management strategy that stalls the realisation of consumer demands indefinitely as incorrect.

In the context of these assumptions, we can further concretise static management: With consumer demands being *permanent* (observation 18) and time-invariant and in the absence of real-time constraints, static management will only be required to take action *upon a change in consumer demands*:

**Definition 29** (Static Management). Upon a change in consumer demands, static management must construct a sequence of actions to be executed by the BMC such that:

- the platform transitions to a new stable state that agrees with the new consumer demands

- no input constraints are violated

No further static management actions must be performed until the consumer demands change once more.

### 4.2 The Objective

As mentioned in the introduction, we wish to explore an approach to a subset of Power and Clock Management that separates policy from mechanism. Now that we have precisely defined said subset in the last section, we can reason about the precise nature of the already mentioned model and mechanisms that we aim to employ for this purpose.

The information our model reflects must be sufficient to support our intended mechanism. In the following two subsections, we are going to first discuss the nature of the mechanism we require before taking a closer look at the model.

#### 4.2.1 The Mechanism

Pooling all the information from our definition of scope (4.1) and chapter 3, we can come to more conclusions about the function and nature of our mechanism:

First of all, we can naturally split the objective of static management as defined by definition 29 into two sub-goals, which we will discuss in more detail in the following two subsections:

- 1. **State Generation**: The process of determining a *new stable platform state* that observes the new consumer demands without violating any input constraints.

- 2. **Sequence Generation**: Generating the sequence of BMC actions that will have the platform transition from the current stable state to this *new stable platform state*.

#### State Generation

To see why this is necessary, we need to remind ourselves of observation 9, which stated that producers are generally arranged in hierarchies. Consumers are mainly supplied by the producers in the lowest level of these hierarchies. The state of the conductors in the upper part of the hierarchy is hence generally transparent to consumers and thus not explicitly constrained by consumer demands. Since the interconnections between different hierarchy levels can be almost arbitrarily complex and convoluted, assigning an appropriate state to each conductor is not necessarily a trivial problem. This is further amplified by the fact that the platform's input constraints (see definition 4) are dependent on the required conductor states.

#### Sequence Generation

Not all of the BMC's actions can be performed in an arbitrary sequence. A good example are commands that are to be transmitted using the I<sup>2</sup>C bus. Before such a command is sent, we must make sure of the following: The intended receiver should be powered, since powered-off devices are usually not responsive to bus commands. Furthermore, as detailed by observation 24, we must ensure that the I<sup>2</sup>C bus is operational. Consequently, we must be able to order the BMC's actions in a manner that observes all such restrictions.

#### **Consumer Demand Generation**

There is another problem our mechanisms must solve. In the definition of static management, we implicitly assume that we are aware of the *new consumer demands*. When we are required to have multiple consumers transition to another power state simultaneously, this is not necessarily the case: Not every platform is built in a manner that allows different consumers to transition to another power state independently of the others. Therefore, we also add *Consumer Demand Generation* to our required mechanisms:

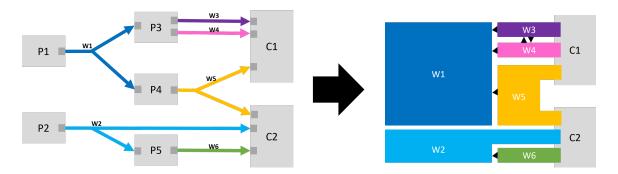

Consumer Demand Generation: Generate a feasible interleaving of all consumer transitions that are requested simultaneously.

#### 4.2.2 The Model

Our model should be able to capture how a platform behaves. It is, however, not supposed to describe the management behaviour of the BMC itself, since it is precisely this behaviour we wish to correctly recreate using our model and mechanisms. We are thus required to devise a model that captures the platform's behaviour from the management perspective of the BMC.

### 4.3 Summary

In this chapter, we have narrowed down the scope of this thesis to static power and clock management. Under the assumption that every platform component is operating as expected, we have concretised our definition of static management. Based on this definition, we have identified three mechanisms necessary to generate correct static management actions based on a suitable platform model.

## Chapter 5

## Modelling the platform

This chapter is concerned with the nature of the platform model we have devised to achieve the objective defined in the previous chapter.

## 5.1 Description of Structures

Before we define our platform model, we wish to introduce some notation in order to unify the descriptions of certain structures found in our model. Since we aim to build mechanisms directly on top of our model, not only is the semantic meaning of the different concepts important, but also the limitations imposed by the representation of the information, i.e. the syntactical aspects. Consequently, we are not merely describing a platform model but rather a modelling language for a platform.

In this chapter, we will represent structures in the following manner: Let S be some structure, composed of attributes  $a_1$  to  $a_n$ . We will provide a schematic overview of the structure in a form as displayed by table 5.1.

As in object oriented programming, we will use the notation  $S.a_1$  to indicate that we access attribute  $a_1$  of a structure S. To increase the readability of subsequent code and formulae, attribute names are kept short. We thus rely on the *designation* column to provide a meaningful and human-readable identifier for the defined attribute.

Occasionally, we will encounter nested structures. We denote the *syntactical structure* of any substructure with its italicised name.

Let Structure be some syntactical structure. We use the notation  $\{Structure\}$  to denote a set of structure Structure and [Structure] to denote an ordered list.

|       | Structure S                                                |  |  |  |

|-------|------------------------------------------------------------|--|--|--|

| $a_1$ | $a_1$ designation for $a_1$ syntactical structure of $a_1$ |  |  |  |

|       |                                                            |  |  |  |

| $a_n$ | $a_n$ designation for $a_n$ syntactical structure of $a_n$ |  |  |  |

Table 5.1: Schematic representation of structures

A schematic overview of an instance I of our structure S would have the following format, whereby terms in <> serve as descriptive placeholders:

|       | I [S]                   |

|-------|-------------------------|

| $a_1$ | $<$ instance of $a_1 >$ |

|       |                         |

| $a_n$ | $<$ instance of $a_n >$ |

Table 5.2: Schematic representation of structure instances

#### 5.2 General structure

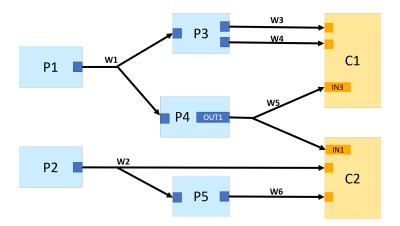

For the perspective of the BMC, the platform is an *ensemble of components* with associated management actions. This natural structure is retained by our model: we describe a platform's behaviour by describing the behaviour of the involved producers (section 5.4) and consumers (section 5.7), along with information on their composition (section 5.8).

This separation of descriptions is possible because every component has but a local view on the platform: both producers as well as consumers (see observation 15) are only aware of the state of conductors that are directly connected to them. Thus, their behaviour can be described in isolation, independently of the whole platform composition.

This model structure has two main advantages: Firstly, a component's behaviour in isolation is easier to understand and is usually reasonably well-documented in its manual. Secondly, we are only required to describe each type of component once, to then be able to build arbitrary platform instances with it.

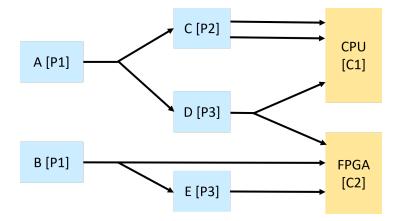

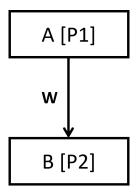

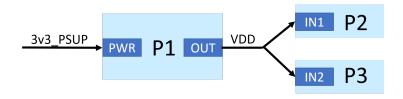

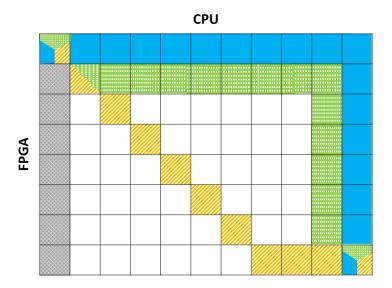

As an example, consider the platform instance depicted in figure 5.1: It features five producer instances A to E and two consumer instances CPU and FPGA. Recalling that we denote the *structure* a particular instance is based on with square brackets [], as defined section 5.1, it follows that instances A and B as well as D and E have been generated by the same producer description P1 and P3 respectively.

## 5.3 Representation of conductor state

This sections aims to discuss the representation of conductor states we use in our platform model.

As detailed in section 3.1, the state of a conductor is given by the values of its physical characteristics. This definition provides a quite natural structure for this section:

In a first subsection, we will think about how to represent a single such characteristic. In a second subsection, we will discuss how to combine representations of several such characteristics to represent the complete state of a conductor.

Figure 5.1: A schematic example of a platform instance, with producer and consumer instances drawn as boxes and the composition information abstracted as black arrows.

#### 5.3.1 Representation of a characteristic

As is the case with most physical quantities, characteristics of conductors are of an inherently continuous nature. However, measurements and regulations performed on them are always of limited accuracy. For this reason, as well as to avoid precision and efficiency concerns associated with real-valued representations, we apply a discretisation to each such characteristic (see table 5.3).

For instance, the typical precision of voltage regulators found on platforms is in the millivolt range. Thus, the voltages across conductors are described by a natural numbers representing *millivolts*. Similarly, the crystals used in oscillator circuits commonly produce a "sine-wave typically ranging from 32kHz to 50MHz". [16]

| characteristic | representation                          |

|----------------|-----------------------------------------|

| voltage        | $\mathbb{Z}$ (interpreted as millivolt) |

| frequency      | N (interpreted as kilohertz)            |

Table 5.3: The discretisation of stable characteristics

### 5.3.2 Representation of state

There are two reasons why the combination of characteristics to the state of a conductor warrants special consideration:

On one hand, as discussed in section 4.2.2, our model must be capable of representing all possible conductor states. Because of this, we need to describe state spaces rather than individual states. For the purpose of this model, we will make use of the most general (and obvious) way to describe such a state space: we simply specify the whole set of individual conductor states present in the given state space. The actual implementation

introduces some abbreviations to improve the conciseness of state space descriptions, see section 8.1.1.

On the other hand, the characteristics of interest to us depend on the purpose of the conductor. As detailed in section 4.1, we are only concerned with *stable* characteristics, which happen to be voltage and frequency. Most generally, the state of a conductor can be described by the value of its low voltage characteristic, its high voltage characteristic and the value of the frequency characteristic with which it is alternating between:

| Conductor State |                             |                  |

|-----------------|-----------------------------|------------------|

| low             | low voltage characteristic  | $\in \mathbb{Z}$ |

| high            | high voltage characteristic | $\in \mathbb{Z}$ |

| freq            | frequency characteristic    | $\in \mathbb{N}$ |

Table 5.4: The Conductor State structure

Remark 30. Of course the shape of the alternation is crucial too, if it is a sine function as with alternating current or clock-shaped; for our purposes, we will simply push this problem to the implementation.

As detailed above, we define the type of a conductor state space as follows:

$State\ Space \subseteq \{Conductor\ State\}$

We will encounter  $State\ Space$  as a description for syntactical structures (see table 5.1) several times in subsequent sections.

However, the State Space S of a conductor W transmitting direct current can be described more concisely: Let E be an element of S. Then E.freq should be 0 Hz and E.low = E.high. Therefore, a single voltage characteristic would be sufficient to describe E. Similarly, the State Space of a conductor transmitting a logical signal could simply be described as a subset of {low (0), high (1)}. To prevent our modelling examples from becoming too unwieldy, we will therefore represent a State Space S as follows:

$$S \subseteq \begin{cases} \mathbb{Z} & \text{if W carries direct current} \\ \{0,1\} & \text{if W is transmitting a logical signal} \\ \{\textit{Conductor State}\} & \text{otherwise} \end{cases}$$

## 5.4 Producer Description

In this section, we take a closer look at how we can describe the behaviour of producers as defined in section 3.2. As already established in said section, producers feature a fixed layout of pins, serving as connections for pre-defined inputs and outputs to the producer.

Because of this, it makes sense to describe a producer's behaviour in an *input/output-centred* fashion.

As we have established with observation 13, the stable states a producer can apply to its output conductors are mostly independent of the history of inputs and commands. For the purposes of this model, this means that we are generally not required to maintain any additional internal producer state. Thus, the descriptions of the behaviour of input and output pins are sufficient to model the behaviour of the entire producer:

Consider therefore a producer with n input pins named IN1, IN2, ..., INn and m output pins named OUT1, OUT2, ..., OUTm. Our producer description will then be of the following format:

| Producer |                     |        |

|----------|---------------------|--------|

| IN1      | description of IN1  | Input  |

|          |                     |        |

| INn      | description of INn  | Input  |

| OUT1     | description of OUT1 | Output |

|          |                     |        |

| OUTm     | description of OUTm | Output |

Table 5.5: The Producer structure

**Remark.** We choose our attribute names to correspond to pin names for reasons of simplicity: In future sections, we will need to be able to retrieve the pin description that corresponds to a given pin name.

As their names indicate, the Input and Output structures referenced in the producer schematic describe individual input and output pins. We will discuss these structures in the next two sections. Unsurprisingly, their focus is on the *states* that connected conductors can or are allowed to attain.

In order to prevent this section from becoming too abstract, we are going to develop the description of an example producer alongside the abstract producer structure. This example producer is the MAX15301 [13], a voltage regulator produced by Maxim Integrated. It produces a single direct current output featuring a voltage that can be specified via PMBus.

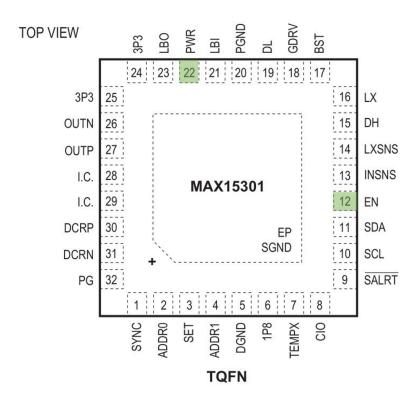

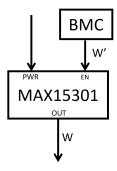

Figure 5.2: pin layout of the MAX15301, taken from its manual ([13])

Looking at the 32 pins the MAX15301 defines (see figure 5.2), the prospect of devising a description of it seems daunting. Luckily, almost all of these pins are irrelevant for our purposes: some just need to be connected to ground in a specific manner to ensure correct operation, others offer points of connection for additional sensors and so on. For us, the important pins (coloured in green in figure 5.2) are:

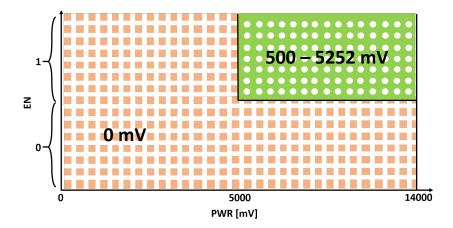

- PWR: an input pin that serves as power supply to the regulator.

- EN: an input pin that serves as a so-called *enable* signal: if the voltage across it is interpreted as HIGH, the MAX15301 will regulate the output voltage to a desired value, and if the voltage is interpreted as LOW it will not.

As an attentive reader might have noticed, we have not identified the output pin whose voltage the MAX15301 is supposed to regulate. The reason for this is that our vision of a producer as a stand-alone integrated circuit starts to crumble a bit here: In a section called *Design Procedure*, the MAX15301's manual meticulously describes how we must combine several of its inputs and outputs with additional capacitors and MOSFETS and whatnot to obtain **the** output the MAX15301 is capable of regulating. The electrical properties of this additional circuitry are far too complex to toss at our platform model (let alone a computer science bachelor student, such as myself), so we take the only reasonable course of action:

We pretend that all this circuitry is a fixed part of the MAX15301 and define an additional, *virtual* output pin **OUT** that provides **the** output.

As far as discussed, the producer instance corresponding to the MAX15301 look as follows:

| MAX15301 [Producer] |                     |  |

|---------------------|---------------------|--|

| PWR                 | < Input instance >  |  |

| EN                  | < Input instance >  |  |

| OUT                 | < Output instance > |  |

## 5.4.1 Producer Inputs

This subsection is concerned with the description of individual input pins to the producer. There are several pieces of information that we must include in such a description:

|     | Input                   |                |

|-----|-------------------------|----------------|

| amr | absolute maximum rating | State Space    |

| mon | monitor functionality   | Monitor Action |

Table 5.6: The Input structure

As detailed in section 3.1, producers define an **absolute maximum rating** for each of their inputs, which must be observed at all times, independently of the states attained by other inputs or outputs of the producer.

Occasionally, a producer offers **monitor functionalities** on some of its connected inputs. These functionalities are especially important in the context of the sequence requirements: In order to correctly time producer commands, our management solution must be able to query the state of conductors to determine if previously issued commands have already taken effect. In section 5.5, we will discuss the usage of these functionalities in more detail.

Now that we have defined the nature of Input structures, we can add the descriptions of the MAX15301's two input pins, EN and PWR.

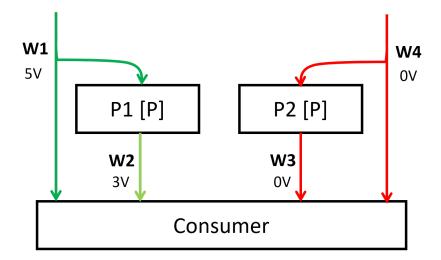

We wish to remark on the consequences of modelling a conductor as a logical signal, using the example of the MAX15301's EN input pin: as already mentioned in the description of this pin, only the interpretation of the voltage across the EN input as HIGH or LOW is of import. It is likely such an EN pin is connected to a GPIO pin of the BMC (see section 3.4.2), which can only be set to either HIGH or LOW. If this were the case, modelling the EN input as a logical signal would be the ideal choice: we convey exactly the right amount of information and need not be bothered with exact voltage values. The drawbacks of this choice are just as obvious: if the EN input is connected to an output whose voltage value needs to be set by the BMC, the EN input description must include information on the interpretation of different voltages and thus cannot be modelled in a logical fashion.

For now, since we consider the MAX15301 in isolation, nothing speaks against modelling it as a logical input. We thus define its absolute maximum rating as the set  $\{0, 1\}$  in

accordance with the State Space abbreviations defined at the end of section 5.3. Since no monitoring functionality on the state of EN is defined, we leave the **mon** field empty.

The maximum absolute rating of the PWR input is defined to be -0.3V to 18V. The PMBus command "READ\_VIN" returns the voltage across the PWR input.

Entering this new information into our schematic MAX15301 instance yields the following:

| MAX15301 [Producer] |                     |                          |

|---------------------|---------------------|--------------------------|

| PWR                 | amr                 | $\{-300, \dots, 18000\}$ |

|                     | mon                 | READ_VIN                 |

| EN                  | amr                 | $\{0,1\}$                |

|                     | mon                 |                          |

| OUT                 | < Output instance > |                          |

## 5.4.2 Outputs

When designing our platform model, we have decided to represent most of a producer's behaviour in the Output structures it defines. The main motivation behind this decision is observation 12: while a conductor might serve as input to several components, it will be connected to at most one output pin of a producer. It thus makes sense to pool as much information as possible at the output pins, rather than composing it from various input pins later on.

In light of this, the distinction between the output pin and the conductor connected to it is becoming somewhat pedantic. In our descriptions, we will therefore occasionally be referring to the unique conductor connected to an output pin as the *output conductor*.

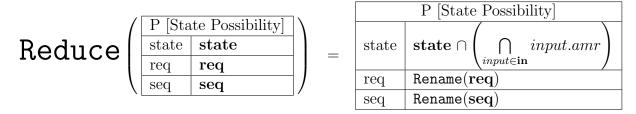

The schematic overview of the Output structure is defined as follows: