#### Master's Thesis Nr. 410

Systems Group, Department of Computer Science, ETH Zurich

Declarative Dynamic Power Management

by

Roman Meier

Supervised by

Daniel Schwyn Dr. Michael Giardino Prof. Dr. Timothy Roscoe

March 2022 - September 2022

#### Abstract

Modern computers feature large power networks that are non-trivial to safely control. The same is true for the Enzian resarch computer [1], which has a power network with 37 voltage regulators, plus a CPU and an FPGA, both of which impose complex requirements on the order in which their power and clock inputs may be operated safely.

Initially, the command sequences to control the Enzians power network were written by hand, but this proved tedious and error-prone. Luckily, prior work in the systems group at ETH Zürich [2][3] has already solved the problem of declarative static power management, but how to manage a dynamic platform that can change unexpectedly remained unadressed.

In this thesis, we develop the design for a dynamic power management solution that is able to keep track of the changes the hardware undergoes, react to faults and other undesireable platform states, and generate command sequences online to steer the platform into a new state. Our solution can read a platform description from a declarative specification and is therefore not limited to one pre-defined platform. We also show experimentally that our plan generation mechanisms are fast enough for online usage.

#### Acknowledgements

I would like to thank my immediate supervisors Daniel Schwyn and Dr. Michael Joseph Giardino for their invaluable support and feedback during these six months, and Prof. Dr. Roscoe for his guidance and the opportunity to work in such an inspiring environment.

Deserving of special thanks is Andrea Lattuada, for his help in clarifying sequencing by partial order.

Last but not least I thank my family and friends for their support and understanding during this occasionally stressful time.

## Contents

| Li | List of Figures |                                            |    |

|----|-----------------|--------------------------------------------|----|

| Li | st of           | Listings                                   | 5  |

| 1  | Intr            | roduction                                  | 7  |

| 2  | Pro             | blem Discovery & Description               | 10 |

|    | 2.1             | Enzian                                     | 10 |

|    | 2.2             | Board Management Controller                | 10 |

|    | 2.3             | Hardware                                   | 12 |

|    |                 | 2.3.1 Classification/Terminology           | 12 |

|    |                 | 2.3.2 Faults & Reaction Times              | 12 |

|    | 2.4             | Dynamic Power And Clock Management         | 13 |

|    | 2.5             | Distinction from Prior Work                | 14 |

|    |                 | 2.5.1 Platform State                       | 14 |

|    |                 | 2.5.2 Reactivity                           | 14 |

|    |                 | 2.5.3 Correctness                          | 15 |

|    |                 | 2.5.4 Optimality                           | 15 |

| 3  | Solı            | ntion Requirements                         | 16 |

|    | 3.1             | Bus                                        | 16 |

|    |                 | 3.1.1 $I^2C$                               | 16 |

|    |                 | 3.1.2 SMBus                                | 18 |

|    |                 | 3.1.3 PMBus                                | 20 |

|    | 3.2             | Timing Requirements & Assumed Stability    | 21 |

|    | 3.3             | Strict Power Dependencies                  | 22 |

|    | 3.4             | Hardware Interface Ordering Requirements   | 22 |

|    | 3.5             | Infrastructure                             | 23 |

|    |                 | 3.5.1 Logging                              | 23 |

| 4  | Apr             | proach 1 — Constraint Satisfaction Problem | 25 |

|    | 4.1             | Background                                 | 25 |

|    |                 | 4.1.1 Compilation                          | 25 |

|    | 4.2             | Modelling                                  | 25 |

|    |                 | 4.2.1 Sequence Generation                  | 25 |

|    | 4.3             | Custom Strategies                          | 26 |

|    | 4.4             | Summary                                    | 26 |

| 5  | Apr             | proach 2 — Planning                        | 28 |

|   | 5.1        | Background                                                        | 28        |

|---|------------|-------------------------------------------------------------------|-----------|

|   |            | 5.1.1 Planning                                                    | 28        |

|   | 5.2        | Modelling                                                         | 29        |

|   |            | 5.2.1 Fault Recovery                                              | 29        |

|   |            | 5.2.2 Whole Model                                                 | 29        |

|   | 5.3        | Summary                                                           | 29        |

| c | Anr        | propel 2 Discrete Event Systems                                   | 31        |

| 6 | 6.1        | proach 3 — Discrete Event Systems  Background                     | 31        |

|   | 0.1        | 6.1.1 Discrete Event Systems                                      | 31        |

|   |            | 6.1.2 Petri Nets                                                  | 32        |

|   | 6.2        | Modelling                                                         | 37        |

|   | 0.2        | 6.2.1 Petri Nets as complete descriptors                          | 37        |

|   | 6.3        | Summary                                                           | 38        |

|   |            | ·                                                                 |           |

| 7 |            |                                                                   | 39        |

|   | 7.1        | Background                                                        | 39        |

|   |            | 7.1.1 Partial Orders                                              | 39<br>40  |

|   |            | 7.1.2 Maximum Independent Set                                     | 40        |

|   | 7.0        |                                                                   | 40        |

|   | 7.2<br>7.3 | High-Level Overview                                               | 40        |

|   | 1.5        | 7.3.1 Model Status and Model Controller Loop                      | 44        |

|   |            | 7.3.2 Model Controller Operation                                  | 52        |

|   |            | 7.3.3 Configuration Management                                    | 53        |

|   | 7.4        | Interface                                                         | 54        |

|   | 1.4        | 7.4.1 Hardware Interaction                                        | 54        |

|   | 7.5        | Present State                                                     | 54        |

|   | 1.5        | 7.5.1 Component-DES                                               | 55        |

|   |            | 7.5.2 Reading Hardware State                                      | 58        |

|   |            | 7.5.3 Restricted Knuselian Component States                       | 59        |

|   | 7.6        | Platform State Transition Manager                                 | 62        |

|   | 1.0        | 7.6.1 Target Platform State Resolution                            |           |

|   |            | 7.6.2 Sequences                                                   | 68        |

|   |            | 7.6.3 Operation                                                   | 74        |

|   | 7.7        | State Transitions                                                 | 76        |

|   | 1.1        | 7.7.1 PET State changes                                           | 77        |

|   |            |                                                                   |           |

| 8 |            | luation                                                           | <b>78</b> |

|   | 8.1        | Scaling and Online-Feasibility of Sequencing and State Generation | 78<br>70  |

|   |            | 8.1.1 Setup                                                       | 78        |

|   |            | 8.1.2 Results & Interpretation                                    | 79        |

|   | 0.0        | 8.1.3 Summary                                                     | 84        |

|   | 8.2        | Simple Correctness of Sequencing and State Generation             | 85        |

|   |            | 8.2.1 Setup                                                       | 86        |

|   |            | 8.2.2 Result                                                      | 88        |

|   | 8.3        | 8.2.3 Interpretation                                              | 89<br>89  |

|   | 0.0        | Summary                                                           | υg        |

| 9 | Con        | nclusion                                                          | 90        |

|        | Future Work      |    |

|--------|------------------|----|

| Biblio | aphy             | 93 |

| A Ev   | nation Artifacts | 97 |

# List of Figures

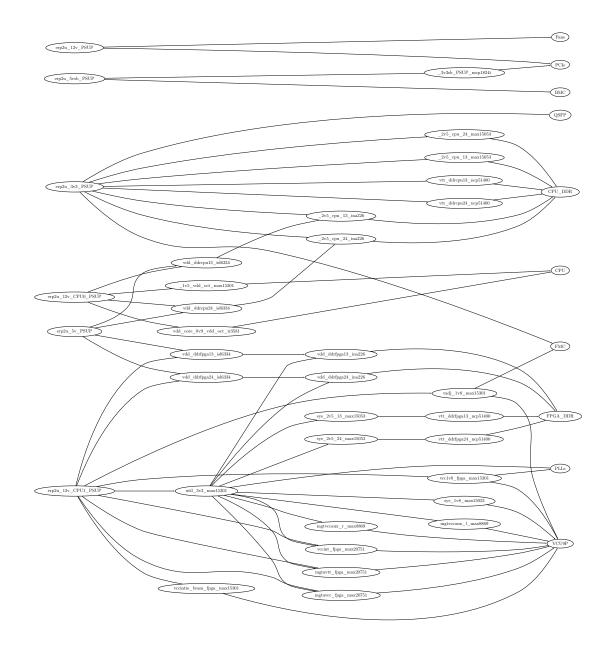

| Inhibitor arcs in three styles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.1        | A simplified view of the complete Enzian power tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 7.1 Initially, we only consider the hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.1        | Timing requirements explainer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24 |

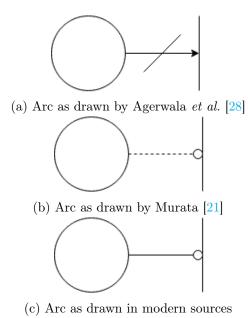

| 7.2 The hardware communicates with the Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6.1        | Inhibitor arcs in three styles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35 |

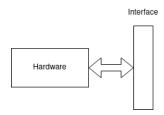

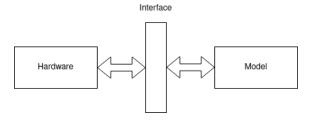

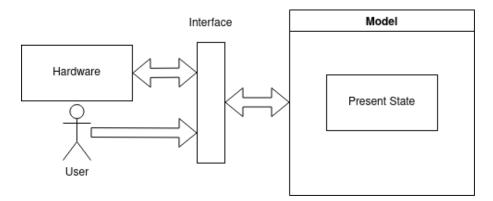

| 7.3 Our model uses the Interface to communicate with the Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7.1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 41 |

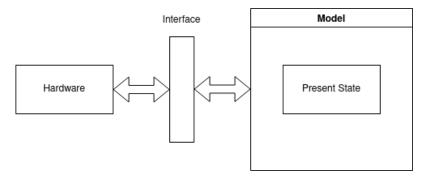

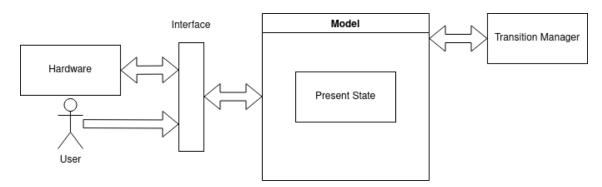

| 7.4 The model must keep track of the "present state" of the hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            | The hardware communicates with the Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 41 |

| <ul> <li>7.5 Users should also be allowed to send the model requests through the Interface. A Transition Manager is in charge of ensuring that the platform transitions from one state to another. It keeps track of the transition progress and future transition targets</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7.3        | Our model uses the Interface to communicate with the Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 41 |

| 7.6 A Transition Manager is in charge of ensuring that the platform transitions from one state to another. It keeps track of the transition progress and future transition targets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7.4        | The model must keep track of the "present state" of the hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42 |

| future transition targets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7.5<br>7.6 | A Transition Manager is in charge of ensuring that the platform transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42 |

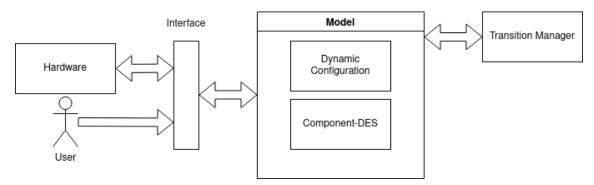

| 7.7 Hardware is too hetergeneous, so we model components as DES. Because these DES struggle with keeping much state, we add a configuration management component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13 |

| component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7.7        | Hardware is too hetergeneous, so we model components as DES. Because these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40 |

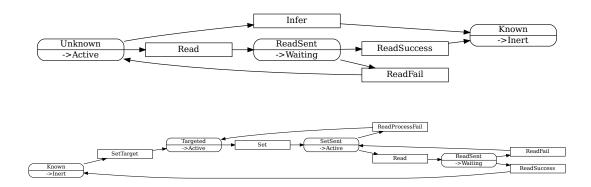

| are squres. Transitions specify the action that must happen for them to fire. States have the model status they imply in their lower half and their name above. "Known" is duplicated and the same state in both figures 50  7.9 Figure showing the possible state incomaptibilities introduced by successive Inputmatches. s <sub>1</sub> is the base-state under consideration. States that can be incompatible are connected with dashed lines. Siblings of s <sub>1</sub> are in gray circles. 66  7.10 Sequence of a platform with a valid target state in T_On but no sequence leading to it. The cycle is marked in red                                                                                                                                                            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 43 |

| above. "Known" is duplicated and the same state in both figures 50 7.9 Figure showing the possible state incomaptibilities introduced by successive Inputmatches. s <sub>1</sub> is the base-state under consideration. States that can be incompatible are connected with dashed lines. Siblings of s <sub>1</sub> are in gray circles. 66 7.10 Sequence of a platform with a valid target state in T_On but no sequence leading to it. The cycle is marked in red                                                                                                                                                                                                                                                                                                                       | 7.8        | Intended PET interaction/actions. States have rounded edges, transitions are squres. Transitions specify the action that must happen for them to fire.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

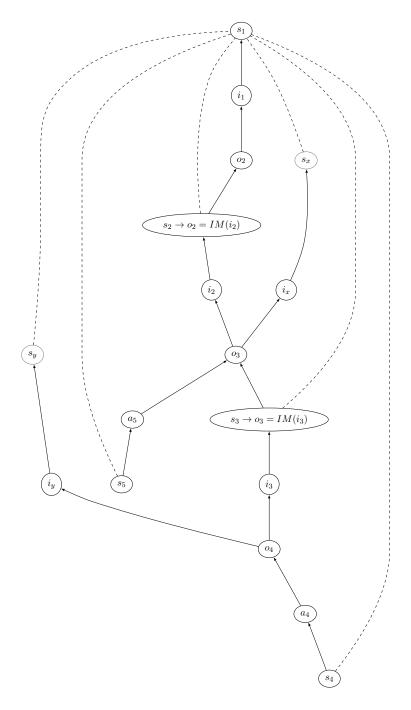

| <ul> <li>Inputmatches. s<sub>1</sub> is the base-state under consideration. States that can be incompatible are connected with dashed lines. Siblings of s<sub>1</sub> are in gray circles. 66</li> <li>7.10 Sequence of a platform with a valid target state in T_On but no sequence leading to it. The cycle is marked in red</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7.9        | above. "Known" is duplicated and the same state in both figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 50 |

| 7.10 Sequence of a platform with a valid target state in $TOn$ but no sequence leading to it. The cycle is marked in red                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| leading to it. The cycle is marked in red                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 66 |

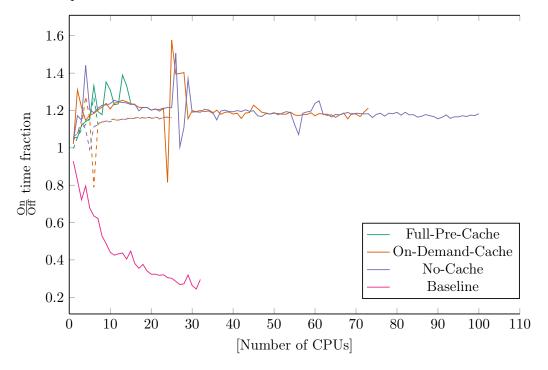

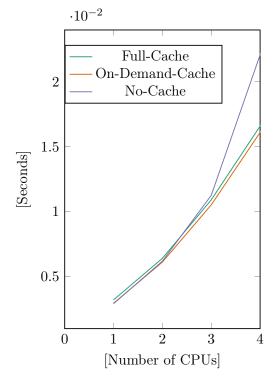

| the undashed lines are from the Precision desktop, expect for the pink line, which shows baseline data. The ratio between sequencing "On" and "Off" seems to increase, but then settle at about 1.15, consistently for sequencing on the Schibenstollo1, as well as on the Precision desktop. Interestingly, for our baseline this reverses, and sequencing "Off" takes much longer, up to an observed 3 times, than sequencing "On". We can conclude that there is no inherent difference in the "Difficulty" of sequencing On or Off sequences, and that instead different implementations can find one or the other much easier to solve for. We also interpret our data to mean that this difficulty ratio converges to a constant, at least for our solution, for sufficiently large | 7.10       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 72 |

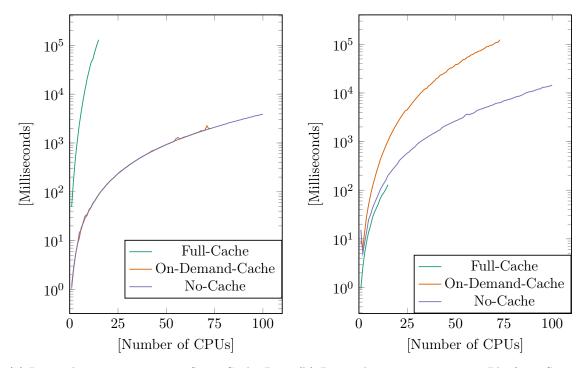

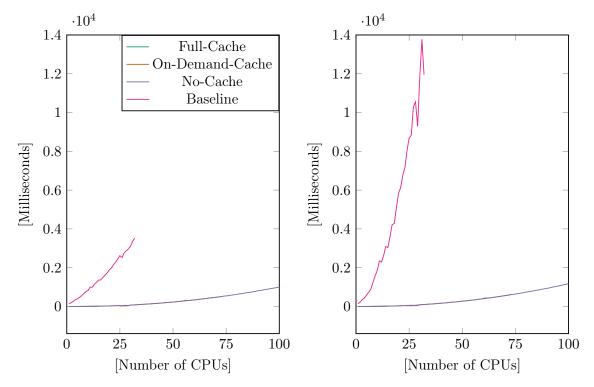

| problem sizes and that a runaway effect is unlikely 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8.1        | the undashed lines are from the Precision desktop, expect for the pink line, which shows baseline data. The ratio between sequencing "On" and "Off" seems to increase, but then settle at about 1.15, consistently for sequencing on the Schibenstollo1, as well as on the Precision desktop. Interestingly, for our baseline this reverses, and sequencing "Off" takes much longer, up to an observed 3 times, than sequencing "On". We can conclude that there is no inherent difference in the "Difficulty" of sequencing On or Off sequences, and that instead different implementations can find one or the other much easier to solve for. We also interpret our data to mean that this difficulty |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | problem sizes and that a runaway effect is unlikely.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 80 |

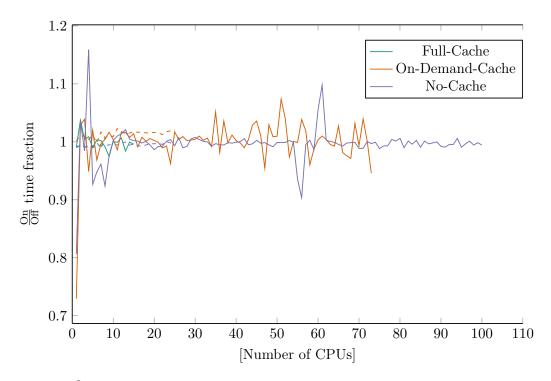

| 8.2 | $\frac{On}{Off}$ state generation time ratio. Dashed lines show data from Schibenstoll01, |    |

|-----|-------------------------------------------------------------------------------------------|----|

|     | the undashed lines are from the Precision desktop dataset. We observe that                |    |

|     | there is almost no consistent difference between generating an "On" vs an                 |    |

|     | "Off" state, barring values we can confidently consider noisy.                            | 81 |

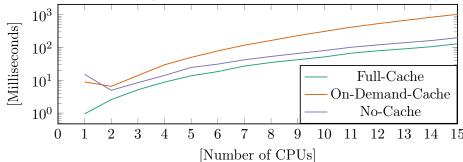

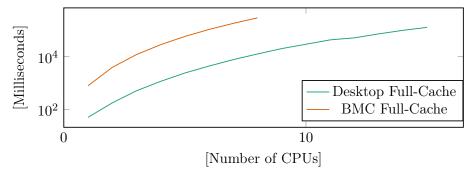

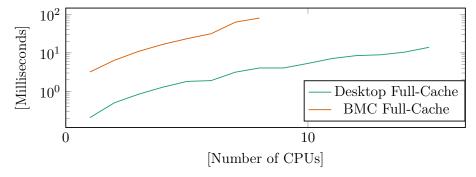

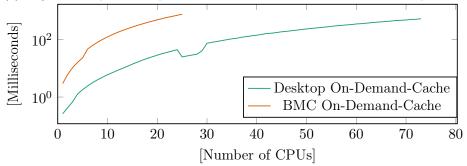

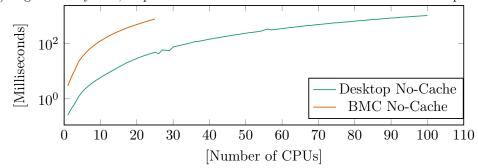

| 8.3 | Cache Precomputation and Target Platform State Calculation times                          | 82 |

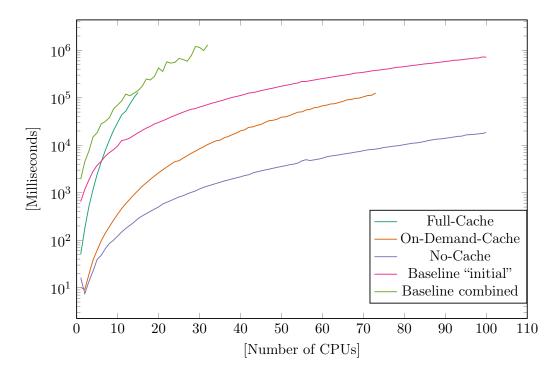

| 8.4 | Logarithmic y axis, Non-baseline are showing Target Platform State Calcu-                 |    |

|     | lation + Target State Cache Precomputation for Turn-on sequence. Baseline                 |    |

|     | is showing times for the two states necessary for both Turn-on and Turn-off               |    |

|     | sequences, as well as a combined value adding the two                                     | 83 |

| 8.5 | Logarithmic y axis, Baseline state computation for "init", "all-on" states and            |    |

|     | a combined measure for both added up. Compare Figure 8.4                                  | 83 |

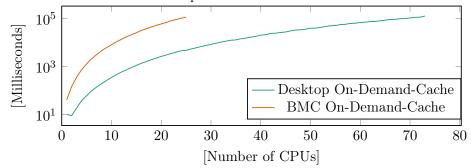

| 8.6 | Comparison showing Sequence Generation times for the Turn-on and Turn-off                 |    |

|     | sequences respectively. Our implementations results very closely track each               |    |

|     | other, and that the baseline takes significantly longer to generate a sequence.           | 84 |

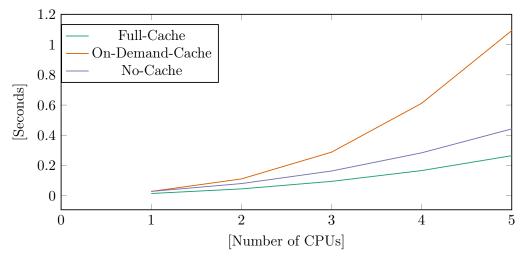

| 8.7 | Comparison of Target Platform State Calculation + Target State Cache                      |    |

|     | Precomputation times on the Zynq BMC and the Precision Dekstop                            | 85 |

| 8.8 | Comparison of Sequence Generation times on the Zynq BMC and the Preci-                    |    |

|     | sion Dekstop                                                                              | 86 |

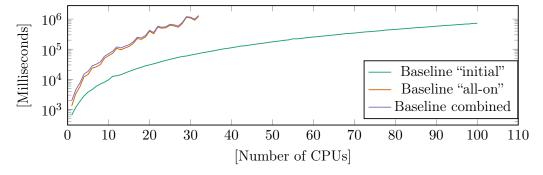

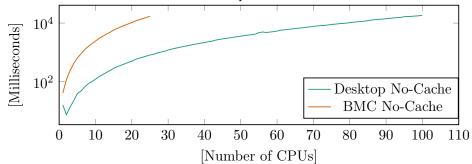

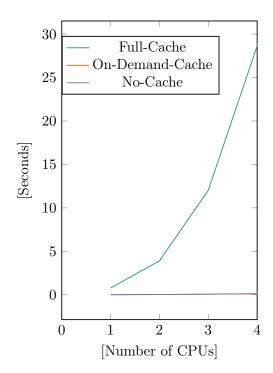

| 8.9 | Comparisons of Total Target Platform State Calculation and Sequence                       |    |

|     | Generation on the BMC for all variants, zoomed in to small platform sizes.                |    |

|     | We see that for effort for the target state cache increases very quickly on the           |    |

|     | BMC, but also that calculating the actual target platform state is always                 |    |

|     | faster than all other variants. For larger platforms, full state precomputation           |    |

|     | is obviously not feasible on the BMC, but a smarter approach where the                    |    |

|     | cache is partially generated on-demand and in the background, or adding                   |    |

|     | heuristics for which target states to generate target platform statest first,             |    |

|     | could preserve the advantages of having a cache, while thinning the pain of               | 07 |

|     | having to compute it.                                                                     | 87 |

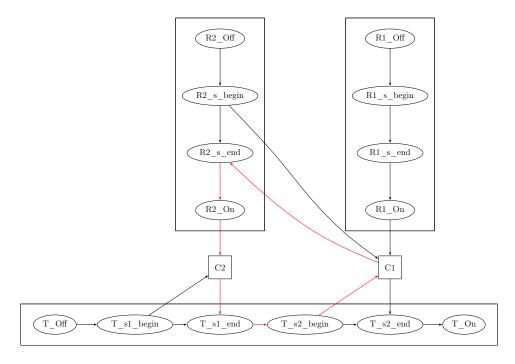

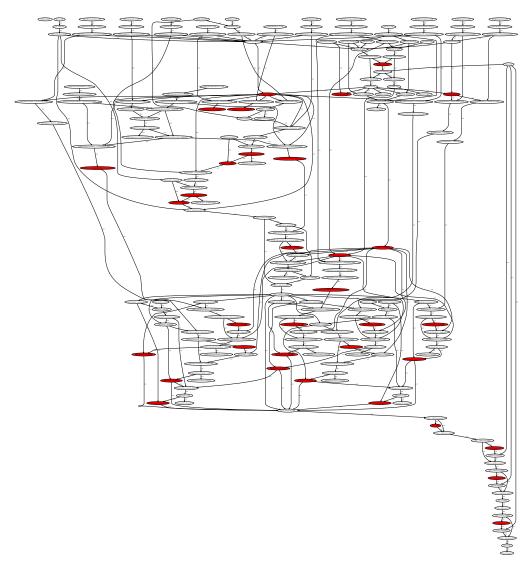

| A.1 | Marked sequence graph for a single ThunderX CPU used in the evaluation.                   |    |

|     | The red vertices are the steps from the baseline output, see Listing 4                    | 97 |

# List of Listings

| 1 | Illustrative subset of the "sanitized" baseline output          | 88  |

|---|-----------------------------------------------------------------|-----|

| 2 | Illustrative subset of the translated sanitized baseline output | 89  |

| 3 | Sanitized baseline output.                                      | 100 |

| 4 | Translated sanitized baseline output                            | 101 |

## Chapter 1

## Introduction

Bernard, if the right people don't have power; do you know what happens? The wrong people get it!

Sir Nigel Hawthorne as Sir Humphrey Appleby – Yes, Prime Minister

Responsible for the management of the complex power networks on modern systems are (Base)board Management Controllers, or BMCs for short. On modern server-class computers the BMC is frequently an independent, fully-featured SOC with unrestricted access to the power network, communications with the host system (for dynamic frequency scaling or similar power-related requests), and even its own network interface. The firmware these BMCs are running is usually proprietary or, in the best case, an open platform like OpenBMC. In either case, the BMC is almost certainly running a complete operating system and taking input from the network interface, usually through a HTTP-webserver.

Considering the extraordinary level of privileged access the BMC has to both security and safety relevant components of the system, one would expect that BMC firmware is implemented with an equally extraordinary level of care and rigour, and that a potential user of such firmware could verify that it would operate their platform safely. However, this is not currently the case. OpenBMC, for example, is a Linux kernel that is running some DBUS infrastructure to allow python and bash scripts to communicate, and the proprietary firmware cannot even be inspected in almost all cases.

To solve these issues, there is an ongoing effort at the ETH Zürich Systems Group to develop trustworthy BMC firmware within the scope of the development of the Enzian research system[1]. The first step, and the one we are concerned with here, is to design and engineer a configurable power and clock management solution that ideally provides strong safety and security guarantees.

Schult [2] tackled the problem of the static management of a declaratively specified platform. Their solution is able to generate command sequences that take a platform from one power state into another, assuming the platform is "stacically stable", meaning it does not ever change its state on its own without explicit instructions.

Knüsel [3] investigated the possibility of generating platform sates and command sequences that are optimal for some goal state, like minimal power draw, but also relied on the static stability of the platform.

This thesis is now an attempt to take the next step: managing a statically unstable platform, a dynamically changing one; to provide dynamic power management. We begin by discussing a few baseline assumptions and building up a common understanding of core concepts, from the top:

The power components present on modern computers are highly heterogeneous, can inhabit complex state spaces and require intricate command sequences to reach those states. Meanwhile, unsafe operation of these power components can cause issues starting from platform instability all the way to causing damage to sensitive, potentially expensive, components. Damaged components, in turn, negatively affect the reliability of the platform or cause it to fail altogether.

At first, any computer is almost entirely inert, bar some coin-battery powered real-time clocks. Once it is connected to power a bare minimum of components usually powers on automatically, like the BMC which is responsible for, among other things, power management of the system and thus also for escaping from this "Partial off" state. A much more pleasing power configuration, especially for a system like Enzian, is for it to be "On". "On" being a shorthand for "Useful". What exactly this means can vary drastically from system to system; for an Enzian a, for a user, maximally flexible "On" state would be if both the CPU & FPGA, their respective DRAM and NIC, and other connected peripheries were in their respective "On", "Useful" states. We now have some notion of distinct power states a system can be in.

What is left to do is to find some way to connect the "Partial Off" state to the "On" state. We call the transition between two power states a "power sequence", made up of discrete steps the platform can take.

The trivial solution to the generation of a power sequence between two states is to read the specifications of all the power components on the system, study the power network that actually connects them, and manually, quite likely by trial-and-error, come up with a sequence of steps that take the platform from the source to the target state. This is also exactly how power sequences for the Enzian used to be generated, but this approach has multiple, major drawbacks:

- 1. Any change to the components on the system requires a manual re-generation of the sequence, including certifying that it actually works.

- 2. Manual work with complicated specifications is error-prone, and while behavioural and safety guarantess can be made for the sequence, doing so usually involves an impractical amount of effort.

Automated tooling is much better equipped for giving these sort of guarantess for an arbitrary instance taken from a large problem space.

Prior work has, as discussed, solved "Static Power and Clock Management", which Schult [2] define like so:

**Definition 6** (Static Power and Clock Management). Static Power and Clock Management is about managing the stable characteristics of conductors. (Schult [2])

Static management explicitly does not concern itself with any kind of deviatory behaviour from what is assumed to be a stable system state. As such, they are not only unable to deal with hardware faults, but the models developed lack the capability to even express

such dynamic behaviour.

For this thesis, we will effectively overload the term "Dyanmic Power Management", which already has an established meaning in the literature. Schult already does so for us:

**Definition 7** (Dynamic Power and Clock Management). Dynamic Power and Clock Management handles exceptional platform events. This includes general platform failures as well as volatile platform characteristics reaching critical levels. (Schult [2])

Peeking ahead to Section 2.4 we define dynamic power and clock management like so:

**Definition 1.1.** Dynamic power and clock management is the process of managing the dynamic power and clock state of a system. Dynamic power and clock management is primarily concerned with the safety of the system under management. In a secondary capacity dynamic power and clock management attempts to reach and maintain a user-defined stable system state. This entails both managing the platform in a non-faulty as well as a degraded, faulty state.

In this thesis, we investigate avenues for solving, and present one possible solution to solve, the dynamic power and clock management problem using a declarative description of the system under management.

## Chapter 2

## Problem Discovery & Description

[...] Hilberry was ready to cut this rope with an axe should something unexpected happen, or in case the automatic safety rods failed.

The first nuclear SCRAM mechanism Allardice et~al.~[4] - The First Reactor

This chapter provides a high-level overview of our problem, introduces necessary background and nomenclature to give a .

#### 2.1 Enzian

Enzian is a research computer designed by and under development at the Systems group at ETH Zurich.

Enzian is a hybrid computing platform with a cache-coherent server-class Cavium ThunderX-1 CPU and a best-in-class Xilinx XCVU9P-3 FPGA, both equippable with large amounts of independent DRAM, and 400GbE or 80GbE network links for the FPGA or CPU respectively.

Enzian was designed, unlike most other computer systems out there, not with a specific use case in mind or constrained by arbitrary cost limits but as a research platform that should be as flexible as possible.

In particular, Enzian's design is optimized for *Coverage*, meaning that it can emulate as much of the design space of systems as possible, and *Openness*, meaning that as much of the system is available for modification as possible.[1]

#### 2.2 Board Management Controller

On many modern computing platforms, especially server systems, we find an SOC dedicated to the management of the rest of the system. This SOC is commonly referred to as the Board Management Controller.

The Board Management Controller is usually responsible for bring-up and dynamic management of the system, and usually provides users with more or less sphisticated remote management options ranging from serial shell access to SSH and web-interfaces. To make

Figure 2.1: A simplified view of the complete Enzian power tree

these remote management capabilities possible the BMC is equipped with a network connection, and many find themselves exposed to the internet directly[5]. Given how critical and potentially vulnerable the BMC is one would expect that it is well-secured and provably so, but it is not uncommon for full Linux distributions to run on these BMCs.

With the development of the Enzian research platform at the Systems group this glaring problem was brought to the attention of the group, leading to efforts to secure the BMC software stack and ideally generate most of the complex, system dependent parts from declarative descriptions.

Initial work has focused on the most immediately critical aspect of BMC funcitonality: power mangement.

#### 2.3 Hardware

We discuss a simple hardware classification scheme as well as how we view the issue of faults & reaction times.

#### 2.3.1 Classification/Terminology

We will avoid using "current" to mean "present", instead opting for "present" directly. We are not going to discuss gifts but will necessarily discuss power and electricity, so swapping these terms is a reasonable choice.

We follow the classification of hardware into three types introduced by Schult [2] and refined by Knüsel [3]:

**Definition 2.1.** Platform A platform is a collection of components and conductors between them.

**Definition 2.2.** Power tree A power tree has the components of a platform as nodes and conductors as edges. For platforms that we are interested in this graph can be represented as a DAG, but in general may be an arbitrary graph.

**Definition 2.3.** Component A component is any node in the power tree.

**Definition 2.4.** Conductor A conductor is an abstract connection between an output and an arbitrary number of input ports. A conductor forms an edge in the power tree.

**Definition 2.5.** Producer A producer is a node in the power tree without any power inputs that are independent of the BMC. A producer may still depend on control inputs from the BMC. In the power tree, a producer would be a "root".

**Definition 2.6.** Controller A controller is a node in the power tree that does not drive any conductors itself, but provides monitoring, alerting and configuration pings.

**Definition 2.7.** Consumer A consumer is a node in the power tree without any power ouputs. In the power tree, a producer is a "leaf".

#### 2.3.2 Faults & Reaction Times

It is in the nature of power faults that if their effects are detectable by sensitive hardware (consumers) then it is already too late.

Ideally, we would like to handle all these faults centrally in the BMC, but because any signal that we might want to send travels at (roughly) the same speed as the fault we have to interpret the fault itself as a signal, which we cannot do, as by the time the fault has reached the BMC and gone through the error handling it has surely reached sensitive hardware as well.

Because the only components capable of both detecting and mitigating power faults are the voltage regulators they must be the ones to establish the fundamental dynamic safety of the platform.

Heimhofer [6] measure alert handler run time at 200 - 800ms for Linux and  $\approx 40$ ms under seL4 and reasons that 40ms is the theoretical limit for an alert handler as implemented due to the fundamental latency induced by I<sup>2</sup>C.

#### 2.4 Dynamic Power And Clock Management

A note for the remainder of this thesis: For brevity, we will frequently only talk about "Dynamic Power Management", but clock management is always implied.

Dyamic power management as found in the literature refers to a completely different problem to the one we are encountering.

While we are concerned with the dynamic management of the system's power network for safety and adaptability, DPM in the literature tries to transition the system into power states such that it consumes as little power as possible overall, as per this definition by Benini *et al.* [7]:

Dynamic power management is a design methodology aiming at controlling performance and power levels of digital circuits and systems, with the goal of extending the autonomous operation time of battery-powered systems, providing graceful performance degradation when supply energy is limited, and adapting power dissipation to satisfy environmental constraints. (Benini *et al.* [7] – p.xi)

This traditional definition of dynamic power management is unfortunately not useful to us. The Enzian is not battery-powered and is not motivated to reduce power consumption, beyond keeping the FPGA and CPU from frying themselves. DPM solutions in the literature also commonly hone in on how to detect which power state is desirable or optimal, and tend to neglect the actual *control* portion of DPM. We will develop our own definition, starting by cannibalizing the traditional DPM definition for the parts that we agree with:

**Partial Definition.** Dynamic power management is the process of managing the dynamic power state of a system.

Ultimately, dynamic power management is not intrinsically motivated. The ideal power state for a system, minimzing all risk without an external goal, is for the platform to be completely powered off. We expand our DPM definition:

**Definition 2.8.** The trivial solution to all power managment is for the platform to be as inert as it can be configured to be. We call this minimal state "off" or "powered off".

**Partial Definition.** Dynamic power management is the process of managing the dynamic power state of a system. Dynamic power management tries to reach a user-defined platform state.

So far our definition basically matches that of static power management. What should intuitively distinguish the two is the idea that DPM is *dynamic*, meaning it reacts to changes in the platform state, be they user-induced or not. This also means that we not only want to *reach* a target state, but also to *maintain* it as far as possible. The decision of when we try to maintain the target state and when we abandon it reveals that we can implement DPM with a goal on the spectrum between

- 1. Quality of Service

- 2. Hardware Safety

**Remark.** "Hardware safety" in this case refers to physical safety, not logical security. By "hardware that is not safe" we don't mean "logically compromised" but rather "in danger of taking physical damage".

If DPM tries to maximise *Hardware Safety* then it may be necessary to compromise *Quality* of Service and usage of the system may be impaired. On the other hand, if we maximise *Quality of Service* we may have to risk our hardware taking damage.

Partial Definition. Dynamic power management is the process of managing the dynamic power state of a system. Dynamic power management tries to reach and maintain a user-defined platform state. A dynamic power management implementation must decide where on the spectrum between maximising "Quality of Service" and maximising "Hardware Safety" its goal lies.

We argue that for most systems, prioritizing hardware safety makes sense. Only very rarely is hardware considered expendable, and the components we are in danger of damaging are potentially difficult or expensive to replace.

However, as the Enzian is a research system, we do not always want to maximize hardware safety either, because that leaves us with a strategy that shuts the platform off completely as soon as anything goes wrong. Instead, we specify that we also want to continue managing the system when it is in a degraded state, and not necessarily always return to the safe "off" state. Part of the motivation behind this is to allow for easier diagnostics when something does eventually go wrong, as a platform that is "off" tells no tales.

**Definition 2.9.** Dynamic power and clock management is the process of managing the dynamic power and clock state of a system. Dynamic power and clock management is primarily concerned with the safety of the system under management. In a secondary capacity dynamic power and clock management attempts to reach and maintain a user-defined stable system state. This entails both managing the platform in a (non-faulty) as well as a degraded, faulty state.

#### 2.5 Distinction from Prior Work

Because there has been prior work in the area of power management, though it concentrated on static management, namely Schult [2] and Knüsel [3], we take a moment to point out some important differences in scope that arise when we can no longer assume static stability of the platform.

#### 2.5.1 Platform State

Prior work did not have to concern itself with the actual state of the platform or how to react to it.

#### 2.5.2 Reactivity

Prior work could assume a completely static view of the world.

This assumption in particular, we argue, has far-reaching consequences: Previously, latency was only a concern insofar as it impacts offline usability of the solution. This means that overall runtime, how it is distributed among solution steps and how runtime varies across executions were far less restricted than they are in our case.

Because we have to deal with actual, dynamically changing hardware we have to make our solution *reactive*, which includes a requirement for low latencies, as we discuss in more detail later on.

#### 2.5.3 Correctness

Prior work - due to it static, offline nature - only had to ensure the correctness of the eventual output of its solutions.

To ensure overall correctness of our approach we also have to, for example, verify the sanity of the declarative platform description.

Prior work took care to never generate a sequence that violated the limits specified in the specification. However, if Prior work were to generate a faulty sequence then the system would simply not turn on. In our case, if we do not generate a correct sequence then the system may cease operating while the user assumes that it is in a stable, safe state.

It is also far less likely that software for dyanmic management is under human supervision, which is almost certainly the case for its static counterpart.

#### 2.5.4 Optimality

Specifically Knüsel [3] concern themselves with a part of the problem state that we so far have left completely unspecified: Optimality.

We do not pursue optimality as a goal in general, but will comment on it if necessary. While we are much more concerned with keeping the platform safe, solutions with equal capability to ensure safety can be compared on optimality of their operation.

## Chapter 3

## Solution Requirements

We can now move one step further: developing a set of ground truths shared by all solutions to our problem.

#### 3.1 Bus

We start out by discussing the bus we use to communicate with the components.

We are going to focus in particular on an observation that prior work made that would increase the complexity of our eventual solution: that some unpowered devices can inhibit the proper functioning of the entire bus.

#### 3.1.1 $I^2C$

SMBus and  $I^2C$  protocols are basically the same: [...]

NXP Semiconductors - I<sup>2</sup>C-bus specification and user manual[8]

$I^2C$  is a protocol for Inter-IC ( $I^2C$ ) control and is popular for low-bitrate on-PCB communication. For complete information about the protocol please see the  $I^2C$  specification [8].

I<sup>2</sup>C is fundamentally a "master-slave" protocol, meaning there is always one "master" controlling the bus. "Slaves" cannot initiate communication by themselves over an I<sup>2</sup>C bus, but must always either wait to be contacted by the "master" or use another method of communication, like an alert line as defined in subsection 3.1.2.

The "master" and the "slaves" are connected by a bus consisting of two lines: the serial data line (SDA) and the serial clock line (SCL). SCL is used to synchronize communication between the master and slaves, while SDA carries actual data bits, either from "slave" to "master" or from "master" to "slave". The I<sup>2</sup>C standard defines four bidirectinal modes: "Standard" (100kHz), "Fast" (400kHz), "Fast Plus"(1MHz), and "High-speed" (3.4MHz).

Due to its popularity but generally low-assurance implementations, there has been work on formally specifying and modelling an  $I^2C$  bus, we refer to Humbel *et al.* [9] for more.

For this thesis, we will end up mostly ignoring the actual I<sup>2</sup>C communication and leaving the issue to some external interface.

There is, however, one aspect of  $I^2C$  that we are very interested in: the problem with unpowered devices.

#### Unpowered Devices

Schult [2] first point out that the I<sup>2</sup>C specification does not actually *specify* the behaviour of a device that has been powered down, in general. In the worst case, this could mean that an unpowered device pulls the I<sup>2</sup>C lines low, potentially disabling the I<sup>2</sup>C bus if *any* connected device is turned off.

The I<sup>2</sup>C standard is an industry standard that has organically grown over time, but we will attempt to shed some light on what it has to say on this issue nonetheless, and give our opinion on what it might mean for our expectations for an "I<sup>2</sup>C-compliant" device.

The I<sup>2</sup>C standard mentions unpowered devices not being allowed to pull SDA/SCL low exactly thrice: Once in relation to the *optional* "Fast-mode":

• If the power supply to a Fast-mode device is switched off, the SDA and SCL I/O pins must be floating so that they do not obstruct the bus lines

([8] - Section 5.1)

And twice in quick succession in relation to another optional feature; software resets after a "general call". A "general call address" is an address used to talk to all connected devices simultaneously. A "general call address" is followed by a 2-byte sequence, and optionally the standard defines a software reset functionality as follows:

**0000 0110 (06h):** Reset and write programmable part of target address by hardware. On receiving this 2-byte sequence, all devices designed to respond to the general call address reset and take in the programmable part of their address. Precautions must be taken to ensure that a device is not pulling down the SDA or SCL line after applying the supply voltage, since these low levels would block the bus. ([8] – Section 3.1.13 – Emphasis ours)

Following a General Call, (0000 0000), sending 0000 0110 (06h) as the second byte causes a software reset. This feature is optional and not all devices respond to this command. On receiving this 2-byte sequence, all devices designed to respond to the general call address reset and take in the programmable part of their address. Precautions must be taken to ensure that a device is not pulling down the SDA or SCL line after applying the supply voltage, since these low levels would block the bus. ([8] – Section 3.1.14 – Emphasis ours)

Neither of these mentions is definitive, however. For Fast-Mode the question arises of whether this refers to Fast-mode capable devices in *any mode*, or devices *in Fast-mode*. Consider the following scenario:

An I<sup>2</sup>C bus, connected to which are exclusively Fast-mode devices, all operating in Standard-mode.

Are any of these devices obligated to let SDA/SCL float when they power down?

Consider also the possiblity of Fast-mode Plus devices, which *must* be downward compatible with Fast-mode:

An I<sup>2</sup>C bus, connected to which are exclusively Fast-mode *Plus* devices, all operating in Fast-mode.

Are these *Fast-mode devices* because they are currently in Fast mode? What if they were in Standard mode?

As for the other two mentions, "Precautions must be taken" is possibly the pinnacle of a non-binding statement and it would not be unreasonable to expect hardware designers to implement these precautions with the same level of care as the I<sup>2</sup>C standard copy-and-pasted the paragraph into two of its sections.

Overall, we are of the opinion that a reasonable I<sup>2</sup>C Fast-mode-or-higher device should definitely never pull either SDA or SCL low, and that all properly designed I<sup>2</sup>C devices in general should be expected to behave the same way, unless there is an obvious reason why they should not – if they are designed to be used in a configuration with only one "master" and one "slave", for example.

For this thesis, we will assume well-behaved I<sup>2</sup>C devices, so that we do not have to consider a Bus inoperable just because a single connected "slave" is turned off.

#### 3.1.2 SMBus

Implementations are encouraged to issue a NACK if the [Packet Error Code] is present but not correct.

SMBus specification [10]

The System Management Bus or SMBus is an abstraction layer on top of I<sup>2</sup>C. SMBus standardises communication over I<sup>2</sup>C such that messages with defined semantics can be passed between SMBus-compliant devices. For complete information about the protocol please see the SMBus specification [10].

SMBus was initially designed with the control of "Smart Batteries" in mind.

#### SMBALERT# and the ARA

See appendix A.2 in the standard.

SMBALERT# is an *optional* interrupt line. In theory, a slave device can pull SMBALERT# low to tell the master that it wants to be spoken to. The alert response address (also mentioned in appendix A.2), which the master can use to find out which device pulled the line low, is specified independently of the SMBALERT# line, so some devices do not react to ARA probes and have to be individually checked for faults when they pull SMBALERT# low.

The standard does specify that

After receiving an acknowledge (ACK) from the master in response to its address, that device must stop pulling down on the SMBALERT# signal. If the host still sees SMBALERT# low when the message transfer is complete, it knows to read the ARA again. ([10] – Appendix A.2)

which suggests that SMBALERT# and the ARA are intended for event notification and not status signalling.

However, some devices insist on pulling the SMBALERT# line low until their fault condition is resolved, so we cannot simply assume that if the SMBALERT# line is low that there is a new fault, independent of the fault conditions we know to exist on the platform.

#### **Unpowered Devices**

As pointed out in subsection 3.1.1 the I<sup>2</sup>C specification does not explicitly stop an I<sup>2</sup>C device from pulling the data or clock lines low when it is turned off, in general. The SMBus specification has this to say on the matter:

When the bus is free, both lines are high. The output stages of the devices connected to the bus must have an open drain or open collector in order to perform the wired-AND function as shown in Figure 4. Care should be taken in the design of both the input and output stages of SMBus devices, in order not to load the bus when their power plane is turned off, i.e. powered-down devices must provide no leakage path to ground. (3. - SMBus Specification Version 3.1[10])

This is a considerable improvement over the I<sup>2</sup>C specification, but the phrasing of "care should be taken" remains too non-commital to be able to hold any non-compliant device actually accountable.

Two other mentions of the problem suggest a stricter interpretation of the above than we argue is necessarily reasonable:

The optional diode shown in the diagram above is for ESD protection. It may be necessary in systems where a removable SMBus device such as a Smart Battery is used. However, circuits as actually implemented must comply with the previously stated unpowered leakage current specification. ([10] – Section 4.3.2)

Because of the relatively low pull-up current, the system designer must ensure that the loading on the bus remains within acceptable limits. Additionally, to prevent bus loading, any devices that remain connected to the active bus while unpowered (that is, their  $V_{DD}$  lowered to zero), must also meet the leakage current specification. ([10] – Section 4.3.3)

The second specification still leaves an imporant detail undiscussed: devices that are not "unpowered"  $(V_D D = 0V)$ , but still "off" in some more abstract sense. Those devices are, even if fully compliant with the SMBus specification, still able to pull the bus low and SMBus does not address this issue.

Much like with I<sup>2</sup>C, we conclude that we can expect reasonably implemented devices not to pull the bus low if they are unpowered or "off", but that the standard once again only provides a weak guarantee for this.

#### 3.1.3 **PMBus**

Plain Text: Characters stored according to ISO/IEC 8859-1:1998 ([A05])

System Management Interface Forum – SMBus specification[10]

The Power Management Bus or PMBus is another abstraction layer on top of SMBus (subsection 3.1.2), defining a protocol specifically concerned with the management of "power converters and a power system". See the PMBus specification [11] for more information.

#### Unpowered Devices

The PMBus specification includes a clear paragraph to ensure that the PMBus is never compromised by a device "involuntarily":

As described [in the] SMBus specification, [A03], the electrical signals of a PMBus device must present a high impedance to the bus when the device is unpowered, during startup until fully powered, and during shutdown once the device can no longer assure the proper signal levels. ([10] – Section 4.3)

This precise phrasing addresses all the concerns we had with I<sup>2</sup>C and SMBus concerning unpowered devices.

Warnings are an indication of a problem that does not keep the device from operating.

**Faults** are severe enough that they may cause the device to stop operating. Most fault responses are configurable.

A device is allowed to either:

- Set fault condition bits and wait to be polled

- Notify the host of a fault condition

#### Alerts

For warnings and faults, PMBus devices may implement *one or neither* of the following notification methods:

- $\bullet$  Using the SMBus SMBALERT# signal

- PMBus devices pull the SMBALERT# line low if possible.

- Directly communicating with the host

PMBus devices become temporary bus masters and send notice to the host.

#### Alert Response Address

PMBus also takes care to clear up any misunderstandings with regards to the Alert Response Address (ARA):

The SMBALERT# signal remains asserted until is cleared. It is cleared when the device successfully transmits its address in response to receiving the Alert Response Address. It is also cleared by a CLEAR\_FAULTS command. ([10] – Section 10.3)

This makes it explicitly non-standard behaviour to not release the SMBALERT# signal after receiving a message on the ARA. However, it does not specify that the component cannot simply re-amble the SMBALERT# signal after having it cleared by an ARA or CLEAR FAULTS command. Persistent faults can still generate multiple signals.

#### 3.2 Timing Requirements & Assumed Stability

To accurately follow the system state we have to consume all events it generates. If events should arrive faster than we can consume them then they must be queued. If they are queued then we either have to be able to determine if incoming alerts/warnings are dependent on other events in the queue, losing time, or simply ensure that the queue does not grow too long.

As we are dealing with a dynamic system that can rapidly evolve we argue that it is critical that any online DPM solution must be able to *react* to changes in the platform state *quickly*.

If the voltage regulators are unable to ensure the system is in a safe state we must make every attempt at saving the system before it takes damage, but because the kinds of faults that may damage the hardware happen much too quickly for this to be feasible (in fact, they travel at the same speed as any message about them) we have to trust the regulators to keep the platform from taking damage in this way and to inform us about the event.

Thus, if the voltage regulators are always able to ensure the system is in a safe, if degraded, state, then we do not need to immediately worry about the hardware taking damage and this argument for the necessity of fast event resolution disappears.

But even then a secondary concern emerges: that of our DPM solution being able to react at all if event resolution does not finish quickly enough.

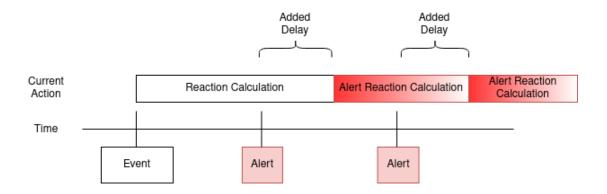

See Figure 3.1a for an illustration of a DPM having to delay reacting to an alert because a previous event resolution takes too long.

This observation relies on the idea that because events can have unpredictable effects on our model platform state, and that we must keep our model platform in sync with the real hardware to be able decide how to react to most events.

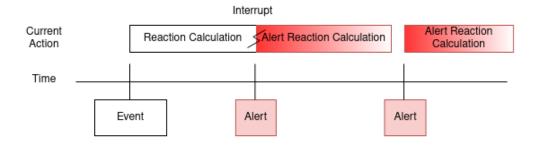

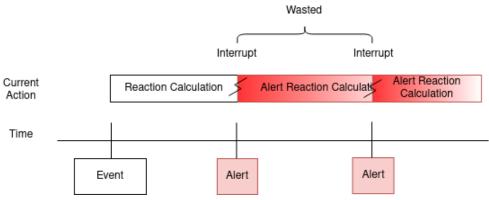

If we assume that some events resolution results are not required for the resolution of some alerts, and that the event resolution can in this case be interrupted, we run into a new problem:

See Figure 3.1c for an illustration of a DPM livelocking itself because it keeps interrupting event resolution due to further events.

Resolving events faster does not solve either of these issues completely, but it is the only way to lessen their effects and to solve them in most instances.

In conclusion, any DPM solution has to assume that the voltage regulators are able to keep the platform safe independently, and it is our responsibility to configure them correctly to achieve this. Second, we must always consume every piece of information the hardware sends us, before we make a new decision. This leads to an assumption that this is even possible, i.e. that the hardware does not flood us with events at a rate where we *cannot* keep up with them anymore. We also assume that we always have the time to read the platform state until we are satisfied that we have synchronized our model with it, because the platform would not be observable otherwise, and an unobservable platform is incredibly difficult, if not impossible, to control. Finally, we argue that it is still important for a DPM solution to react quickly to hardware changes for a better user experience, and to give our DPM solution a wider range of hardware-event-rates that it can still control.

#### 3.3 Strict Power Dependencies

Dealing with the actual components making up the power network has the unusual consequence that most of the components we would like to model depend on another component to function at all.

Consider voltage regulators A and B with their respective models  $A_m$  and  $B_m$ . We make no assumptions about how these models are realized, only that they accurately model their target's behaviour and somehow allow their simulation i.e. have predictive capabilities.

If voltage regulator A is connected to voltage regulator B's VCC, then A must be in a state where it delivers power to B or cannot transition into a useful state.

This kind of dependence is not actually unusual. The whole point of the modelling techniques we consider as approaches is to describe the situation where one thing happening depends on another thing having happened in the past, or not having happened yet.

Consider now the following scenario:

A is delivering useful power to B, which cannot function without it. B is in an arbitrary internal state and  $B_m$  is in sync with B. Voltage regulator A suddenly stops delivering power. As B depends on A for power it immediately turns off.

$B_m$ , to account for B's sudden change of state, must immediately reflect this. In fact,  $B_m$  must make provisions for B losing power whenever it depends on it, which for any useful device is the case for most of its model space.

This only gets worse as the power network grows in size and more and more components rely on each other for power, depending on the model, a component may have to explicitly react to any one of its parents in the power tree changing.

For explicitly state-based, simple modelling techniques this leads to an explosion in the number of state transitions that have to be accounted for.

Note that the same thing happens when modelling the complete internal state space of a regulator.

#### 3.4 Hardware Interface Ordering Requirements

Seeing that we can receive distinct categories of events with very different immediate criticality, alerts as "Warnings" or "Faults" or expected measurements, it may seem like a good idea to prioritize alerts over common events.

There is, however, a fundamental necessity in *considering* incoming events in the order that reflects the changes the hardware went through accurately, which for all practical